主题中讨论的其他器件: CSD、 CSD19531Q5A、 CSD19533Q5A、 CSD19534Q5A、 TPS40170

我们将 CSD18537NQ5A 用作基于 TPS40170RGYR 平台的降压转换器上的高驱动 FET。

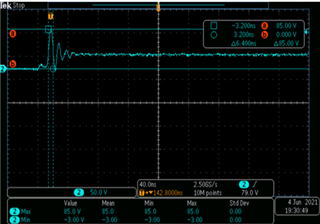

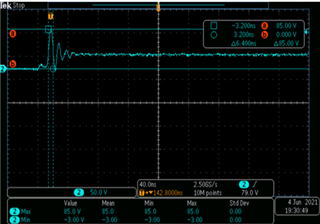

85V 6nSec 接通脉冲是否会对器件造成损坏?

Jojo

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

我们将 CSD18537NQ5A 用作基于 TPS40170RGYR 平台的降压转换器上的高驱动 FET。

85V 6nSec 接通脉冲是否会对器件造成损坏?

Jojo

你好、Jojo、

感谢您关注 TI FET。 只要超过绝对最大额定值、就会有器件损坏或故障的风险。 脉冲宽度很短、但波形上有明显的振铃。 您如何以及在哪里进行测量? 示波器探针应尽可能靠近 FET 引脚、并具有非常短的接地连接。 请访问我们 的支持与培训 页面、您可以在其中找到 有关同步降压转换器振铃减少的应用手册。 如果您需要进一步的帮助、请告诉我。

此致、

John Wallace

TI FET 应用

你好、Jojo、

感谢您提供更多信息。 CSD18537NQ5A 是一款60V FET。 TI 还生产出采用相同5x6mm SON 封装的80V 和100V 器件。 两个最接近 CSD18537Q5A 的 FET 导通电阻为 CSD19534Q5A (VGS = 10V 时为15.1m Ω、13m Ω)和 CSD19533Q5A (VGS = 10V 时为9.5m Ω、导通电阻为9.5m Ω)。 根据您之前的帖子中的相位节点波形、低侧 FET 会看到过多的 VDS。 它也是60V FET、100V FET 是 CSD19531Q5A (6.4m Ω 与6.8m Ω)。

波形显示输入电压约为30V。 通常、这需要40V 或60V FET、但开通时的过冲大于输入电压的2倍。 开关节点振铃过大、我对此感到惊讶。 您共享的波形有哪些条件? 您的要求是什么:VIN、Vout 和 Iout? 在开关节点上似乎有一个 R-C 缓冲器。 您是否尝试调整这些值以减少振铃? 您还可以调整 R89的值以降低高侧 FET 的导通速度。 是否可以为高侧 FET 添加串联栅极电阻器?

TPS40170控制器应具有足够的击穿保护、并且 FET 经过优化、可防止由于栅极上的 CDV/dt 感应电压而导致误导通。 当超过 BVDSS 时、低侧 FET 更有可能发生雪崩。 波形不会在峰值处显示任何削波、这可能是因为脉宽很短。 TI 对我们的 FET 进行单脉冲雪崩-而不是重复雪崩的评价。

谢谢、

John