您好,

在什么情况下 、此配置上可能会发生"击穿"情形、从而可能损坏高驱动或低驱动 FET?

谢谢你。

Jojo

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Tim、

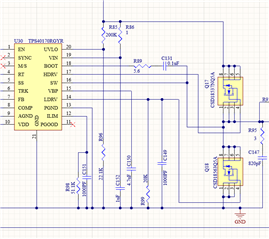

感谢你的答复。 TI 数据表中存在1欧姆电阻器的原因或其他用途是否? 还是仅仅为了实现布局灵活性? 或者之前在 我们之前的评论中解释过我可能无法赶上... 另外一点、我们是否可以说 TPS40170具有内部击穿保护、而不仅仅是从旧数据表中写入的保护? 最后、但同样重要的是、关于控制机制、我们采用了一个外部微控制器、通过 VPROGClamp 注入控制信号传输到 FB 控制引脚、绕过正常输出反馈环路、 这是否会导致潜在的不稳定性、从而可能导致击穿情况、从而在 HDRV 或 LDRV FET 进入突发模式区域时损坏它。

谢谢你。

Jojo

你好、Jojo、

栅极驱动器设计为在所有条件下都不会重叠、与控制无关。 但是、如果 SW 电压具有高 dv/dt、它可能会电容耦合到低侧栅极、并在 SW 转换期间导致电压下降(所有降压设计都是这种情况)。 因此、只需确保这一点在低侧栅极上不明显(LDRV 上的尖峰肯定应保持在 FET 的米勒平坦电压以下、因此 LDRV 与 GND 之间的电容会改变漏极与栅极之间的电容分压比)、

1欧姆最初用于输入电压纹波滤波、但我的理解是它可能会导致 RC 延迟而不是高侧电流感应-这是用于失效防护电流限制(主要 OCP 功能是使用低侧 FET)。

此致、

Tim