主题中讨论的其他器件: LM5145、 LM25149-Q1、 CSD18533Q5A、 LM5146-Q1

您好!

我设计了控制器、无法使其通过 EMC。 我已经尝试向输入和输出线添加铁氧体、更改 CBoot、以及调整缓冲电容器和电阻器的值。 我不知道要尝试什么。 现在、我意识到需要移除 SW 节点中的过孔、并且布线需要在顶层运行。 将铜从底层上刮走并切割底部迹线、然后将其替换为顶层的导线、这一点没有什么不同。 我还添加了较小的电容器、以便对稳压器的输入和输出电容器进行去耦、而不会产生任何影响。 开关节点中有振铃、我无法进一步抑制。 我已关闭 PCB 上的所有其他子系统、因此噪声来自该器件。 如果您需要其他信息、请告诉我。 感谢您提供的任何帮助。

控制器参数:

输入电压40V

最大输出电压9.25V

电流限制8.5A

该控制器主要以限流模式运行。

原理图

顶层

底层

层叠

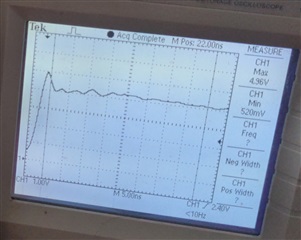

开关节点(探头10X)

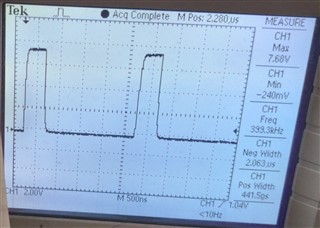

高侧栅源极

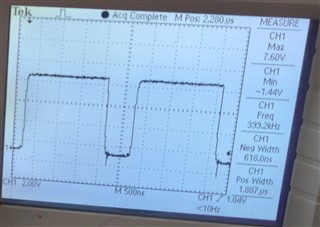

低侧栅源极

EMC 测试报告

e2e.ti.com/.../FON2.5_3575E389346C6856_RE_4B6DD58BA5624A54_20210330.pdf