主题中讨论的其他器件: UCC28730

您好、E2E、

图15显示了四个运行区域。 在区域3中、开关频率保持恒定(25kHz)、而开关关断时的峰值电流控制在其最大值的25%至100%之间。 在该区域、 我们的客户 转换器显示屏在输出电压中具有一些低频振荡(频率~500Hz、+12Vdc 上的200mV p-p 正弦波)。

在图14的磁化复位时间内、这个区域的稳定性是否依赖于 Vs (引脚6)上信号的斜率下降? 如果"是"、为确保良好的稳定性、斜率范围是多少?

此致、

卡洛

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、E2E、

图15显示了四个运行区域。 在区域3中、开关频率保持恒定(25kHz)、而开关关断时的峰值电流控制在其最大值的25%至100%之间。 在该区域、 我们的客户 转换器显示屏在输出电压中具有一些低频振荡(频率~500Hz、+12Vdc 上的200mV p-p 正弦波)。

在图14的磁化复位时间内、这个区域的稳定性是否依赖于 Vs (引脚6)上信号的斜率下降? 如果"是"、为确保良好的稳定性、斜率范围是多少?

此致、

卡洛

您好、Carlo、

UCC28704反激式控制器的稳定性不取决于退磁期间 VS 信号的下降斜率。

在退磁间隔之后保持一个相对陡峭的拐点非常重要、在该消磁间隔中、如 图13中所示对 VS 进行采样。

一个"软"拐点、例如 VS 上出现的杂散电容、可能会在一个周期到另一个周期的采样中引入轻微变化、这可能导致客户观察到的500Hz 振荡。

我建议查看 VS 输入端的 PCB 布局、以确保最小布线长度和连接 GND 和其他信号的最小电容。

此致、

Ulrich

您好 Ulrich、

感谢您对此进行深入研究。 我们的客户存在以下问题:

我的问题更多地涉及这些运行模式的稳定性标准、特别是:引脚3上的波形的哪个部分会影响区域3中的稳定性。 我们看到+12Vdc 输出上有200mVp-p 300~500Hz 正弦波。 我们需要噪声和纹波电压低于20mVp-p Vs (PIN6)处该波形的哪一部分将使我们了解交流纹波的根本原因。

我尝试概述 UCC287xx 系列、即哪些器件具有哪些功能。 我感兴趣的特定功能:

初级侧调整(消除了光电耦合器)、

2.导通时 ULVO 阈值大于15V,关断时阈值小于8V (使器件能够直接将 MOSFET 栅极驱动至大约10V 峰值)。

3.谷底开关(以减少开关损耗)。

4.电缆补偿-不需要。

这些都是 UCC28704的功能、但鉴于我在这一不稳定问题上的经验、我想添加另一个功能:可以观察到控制律输出。 理想情况下、我想要的是 UCC28704、但采用7或8引脚封装、其中一个额外引脚上提供了模拟器控制律信号。 此类设备是否存在? 如果没有、是否有适合的近亲? 例如:28730。

当输出上有2个470u 电容时、Vout (200mVp-p 300~500Hz 正弦波)上会发生不必要的振荡(请参阅原理图碎片、C5、C6)。 卸下其中一个电感电容器后、此问题将停止。

当出现不稳定时、与不存在纹波的情况相比、脉宽和峰值 MOSFET 电流在更宽的范围(从1.42到3.89us)内变化迅速。 附加的波形显示了短脉冲和宽脉冲的示例、布线为:

CH1 = Vsense 绕组

CH2 = Vs (引脚6)

CH3 = UCC28704 Vcc (引脚2)

我的参考资料:TEK0109、0110。

比较有无问题的运行情况:我没有注意到在去磁放大周期结束时与的"拐点"之间有任何显著差异。

如果您的假设正确、那么确保稳定性需要多大程度的膝部"硬度"?

这些波形是在相同的负载条件下获得的、即259mA (大约为满负载的25%、在区域3中)。 这里是在更长的时基条件下、在相同的线路(200Vdc)和负载条件(+12V、259mA)下获取的另外两个波形、其中存在不需要的交流纹波。 一个波形是较短的 MOSFET 导通时间、另一个波形是较长的导通时间(我的参考文献:TEK0099、0100 RESP)。

CH1 = Vsense 绕组

CH2 = Vsense 绕组上 dv/dt 缓冲器的 V CAP

CH3= UCC28704 Vcc (引脚2)

Ch4 = MOSFET 漏极电压

出现过大纹波时的输出电压波形。 输出电压的标称值为+12Vdc。

当负载介于满负载的20%和40%之间时(满负载为1.0A)、就会出现此问题。 它在很大程度上取决于输入电压。

请参阅随附的文件。

e2e.ti.com/.../UCC28704.zip

感谢您的帮助。

此致、

卡洛

您好、Carlo、

在 VS 上的'scope 探头本身将增加显著的电容、这可能会影响拐点特性。 VAUX 波形本身显示了 Demag 拐点的足够清晰度、可实现良好的稳定性。 在 VS 上进行探测可以软化该拐点、并 将稳压电压稍微升高。 我们强烈建议不要将探针直接放在 VS 上;而是使用 VAUX 波形并通过电阻分压器对其进行缩放。

UCC287xx 系列的反激式控制器都没有可直接查看的控制法律。 根据实际的 Ippk 和开关频率以及 IOCC 下的最大设计 Ippk 和最大设计频率、可以推断出该定律中的运行点。

鉴于满负载的20~40%负载会出现此问题、我认为不稳定可能与区域3和4之间断点附近的运行相关。 采样中的小干扰可能会将运行推向更高的定律或更低的定律、而响应延迟可能会使干扰加剧为振荡。 移除一个输出电容器似乎与此相对应、因为较低的 Cout 会使干扰看起来更大、环路响应速度更快、从而避免过冲并抑制振荡趋势。 也许只使用1个470uF 电容器是解决稳定性问题的方法。 将输出纹波降至20mV 可能需要一个后置 L-C 滤波器级、但该滤波器级应小于另一个470uF 电容器。

此致、

Ulrich

您好 Ulrich、

以下是我们客户的回应:

[引用 userid="64834" URL"~/support/power-management-group/power-management/f/power-management-forum/1003306/ucc28704-frequency-and-amplitude-modulation-modes/3710137 #3710137"]VS 上的探测可以使该拐点软化、并 使稳压电压略微上升。 我们强烈建议不要将探针直接放在 VS 上;而是使用 VAUX 波形并通过电阻分压器对其进行缩放。 [/报价]是的、我知道该节点(Vs)对电容很敏感、包括任何探头的电容。 请注意、我们的通常做法是将引线式电阻器(通孔器件、约为1至2千欧)焊接到节点上、并将示波器探针连接到该电阻器上、从而减少任何探针 C 的影响。我们使用探针、尖端 C <15pF (x10、200MHz)。

无论是否连接了示波器探头、器件在输出电压纹波和输出电压调节方面的行为都保持不变、这使我们确信示波器探头不会显著影响 UCC28704的运行。

问题在于、一个470uF 电容器没有额定纹波电流来提供此应用所需的使用寿命。 最初选择2个470uF 电容器的原因是需要确保电容器寿命不会因纹波电流而缩短。 任何给定的电容器都具有 ESR 值、这会导致纹波电流导致自发热、 这会因封装的热阻抗(取决于 E-cap 的大小)及其安装(焊接到接地层、气流、靠近热源等)而导致温度升高。

我们的问题是、如果 e-CAP ESR 影响稳定性、则需要了解此问题、以便我们可以采取适当的步骤来确保整个工作范围内的稳定性、例如:选择合适的电容器或引入额外的 R

是的、我们的设计已经包含一个后沿 L-C 滤波器级、但其截止频率(-3dB)约为5kHz。 由于 MOSFET 切换至可接受的水平、它确实会降低纹波、但不会滤除我们看到的低频纹波(300Hz 至500Hz)。

此外、我们的客户正在寻找 Billy Long、当我查看我们的目录时、他似乎不再与 TI 合作。

我问 Billy Long 的原因是、当我搜索 UCC287xx 器件系列的概述时、出现了这种情况。 因此、我似乎还没有一个文档(例如选择图)来解释该系列中的器件(相似性和差异)、从而可以轻松选择 UCC287xx 系列中的哪一个成员最适合给定的应用。

以下是此选择图之所以重要的一个示例:UCC28704使用传感绕组来测量**两者**:

(a)输出电压和(b)输出电压。

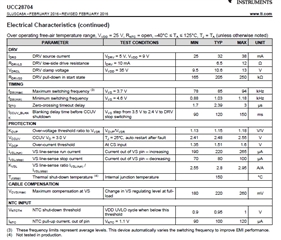

为了测量 Vline、UCC28704对 MOSFET 导通时从 Vs 引脚拉出的电流进行采样。 该电流由设置用于设置 Vout 的分压比的电阻器设置、该电阻器还设置 Vline 启动/关断电压、请参阅数据表参数:

VS 引脚的 IVSL (RUN) VS 线路感测运行电流电流–增加= 220μA μ A 典型值

VS 引脚的 IVSL (STOP) VS 线路感应停止电流–降低= 80μA μ A 典型值

(请参阅随附的数据表相关部分的屏幕截图)。

由于 Vs 引脚具有多种功能、因此这些电阻器的值不可自由选择(只有特定范围的值才能满足所有要求)。 在我们的案例中、这些 R 值非常高、会导致 Vs 引脚上的信号具有相当高的阻抗、这使得它对该引脚上的任何杂散 C 都很敏感、这可能会导致我们看到的问题。

因此、我想查找的是 UCC287xx 系列中的一个产品、它以不同的方式感应 Vline、以便我们只能根据设置 Vout 来自由选择电阻器值、 因此、我们可以使 Vs 处的信号阻抗更低、以降低 Vs (引脚6)处任何 C 的影响。 我希望有一个易于使用的选择器图表来实现这一目的。 该系列的一个成员看起来很有希望、那就是 UCC28730、它与 Vline (HV 引脚)具有单独的连接。 我最初以为这是我们问题的解决方案、因为我认为它通过 HV 连接测量 Vline。 唉、在仔细阅读数据表后、我意识到它的感应方式与 UCC28704相同、连接到 Vlne 仅为芯片启动供电。

所以我的问题仍然没有得到解决。

感谢您的进一步帮助。

此致、

卡洛

您好、Carlo、

UCC287XX 系列的所有产品都使用 VS 输入进行输出感应和线路电压感应(实际上、是大容量电压感应)。 由于可用引脚数量有限、因此需要多功能、这会限制电阻器值的选择。

具有 HV 引脚的器件包含一个高压 JFET、用于加快启动速度和降低待机功耗。 它不执行任何其他功能。

PSR 控制器的稳定性不取决于输出电容器的 ESR。 在 Demag 拐点选择采样、这正是因为在这种情况下、绕组电流变为零、ESR 产生的任何纹波电压的贡献也为零。 在这种采样方法中、稳定性主要是为了避免反馈路径中的延迟、这会导致控制器对过去已经很明显的情况做出反应。 这就是如何增强低频纹波的原因、因为环路试图补偿已经沿另一个方向发生的输出变化太晚了。

我对额外470uF 电容器的担心是、当控制器尝试针对其采样值进行调整时、它可能会导致 Vout 变化更慢。

我知道纹波电流是一个问题。 由于两个 Cout 位置可用、因此可能可以并联使用两个220uF ~270uF 电容器来共享电流。

在具有10千欧阻抗的网络中隔离仅2K 的15pF 示波器探头可能不足以在所有情况下屏蔽 VS 免受其滤波影响。 由于即使没有连接探针、电路的行为也是相同的、因此我同意它不能是导致延迟的探针。

PCB 布局杂散电容仍然需要考虑。 设计指南是将分压器的底部和顶部电阻器放在引脚上、以最大程度地减小走线长度及其后续电容。

为了测试 VS 上的电容效应、我建议将 两 个 VS 电阻器减小5~10X 以减少任何 RC 时间常数。

这将使调节保持不变、但它允许以低得多的大容量电压启动。 这与测试目的无关、您仍然可以应用正常输入来启动。 如果波纹没有改善、我认为减少 Cout 可能是唯一的选择。 没有其他可调整的内容。

最后一点、尝试将 LC 滤波器的输出电感器短路以进行测试。 如果它与470响铃、您可以更改它的值或在它上面添加阻尼器。 如果没有效果、我们回到上一段。

此致、

Ulrich

您好 Ulrich、

以下是我们客户的回应:

[引用 userid="64834" URL"~/support/power-management-group/power-management/f/power-management-forum/1003306/ucc28704-frequency-and-amplitude-modulation-modes/3713605 #3713605)]最后一件事是、尝试缩短 LC 滤波器的输出电感器以进行测试。 如果它与470响铃、您可以更改它的值或在它上面添加阻尼器。 如果没有效果、我们回到上一段。 [/报价]我们已经消除了任何输出滤波器组件之间的谐振、将其作为此问题的根本原因。

[引用 userid="64834" URL"~/support/power-management-group/power-management/f/power-management-forum/1003306/ucc28704-frequency-and-amplitude-modulation-modes/3713605 #3713605"]我对额外470uF 电容器的担忧是、当 contol 尝试调整其采样值时、它可能会导致 Vout 更缓慢地变化。这表明稳定性取决于 Vout 的变化率、后者取决于 C 和其 ESR (只是时间常数)。 这意味着存在 C 的上限值和 ESR 的下限值、超过该值可能会发生不稳定。 请与我们分享计算稳定性裕度对 C 和 ESR 的依赖性所需的信息。

[引用 userid="64834" URL"~/support/power-management-group/power-management/f/power-management-forum/1003306/ucc28704-frequency-and-amplitude-modulation-modes/3713605 #3713605)]我知道纹波电流是一个问题。 可能可以并联两个220uF ~270uF 电容器来共享电流、因为有两个 Cout 位置可供使用[/引用]是的、我们已经探讨了这个选项。 问题是部件必须满足**所有**对 C、ESR、纹波电流额定值和温度的要求。 考虑到所有这些因素、可以显著缩小合适元件的范围、我们的供应商根本无法提供合适的器件。

如果我们更好地了解 C 和 ESR 的限制、那么我们也许可以扩大合适组件的范围、从而更幸运地采购这些组件。 到目前为止、我们所能做的就是了解工作原理(例如1 x 470uF)、并选择并联电容器以提供相同的 C 和 ESR 值。

是的、除了更好地了解 C 和 ESR 对稳定性的影响之外、似乎唯一的选择是执行此测试。

感谢您迄今提供的帮助。

此致、

卡洛

您好、Carlo、

a 我之前提到过、由于 UCC28704在降压电流变为零时对 VOUT 进行采样(通过 VS)、因此输出电容器的 ESR 对稳定性没有影响。 ESR 仍然是纹波电压的一个因素、但无需匹配任何器件即可实现稳定性。

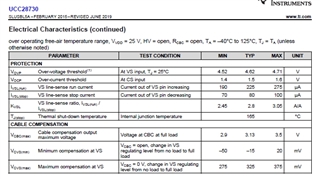

数据表中显示的稳定性标准是公式(5)、第14页。 1x470uF 和2x470uF 均符合此标准。

我发现另一个限制:COUT > 3000~5000uF 可能会导致1.5kHz 的振荡、但这不会影响您的设计。

所有面值参数都表明您的设计应该是稳定的。 由于它不是、设计中必须有一个不需要的和未表征的寄生参数。 我怀疑这个寄生电容是 VS 节点上的杂散电容、这会在环路响应中增加一个延时时间。

我认为观察到的振荡表明了这种时间延迟。

将 Cout 减少一半会使其 Vout 采样 变得灵敏两倍、因为基于最后一个采样的占空比变化 可以使 Vout 移动两倍、并且在下一个采样中更容易检测到。 这有助于抑制 由于时间延迟而产生的振荡。

我期待在 输出电压为 2x470uF 时 VS 上的 Rvs1和 Rvs2大幅降低的测试结果。

此致、

Ulrich

您好 Ulrich、

以下是我们客户的回应:

[引用 userid="64834" URL"~/support/power-management-group/power-management/f/power-management-forum/1003306/ucc28704-frequency-and-amplitude-modulation-modes/3718081 #3718081"]我发现另一个限制:COUT > 3000~5000uF 可能会导致1.5kHz 的振荡、但这不会影响您的设计。 [/报价]请分享公式以计算将导致此1.5kHz 振荡的 Cout 值。 您引用的值(3000~5000uF)是否取决于输出电压? 请注意,我们的设计是+12V,所以我怀疑这将意味着这将*减少*出现此振荡的 C 值(次级绕组和感应绕组具有相同的匝数,因此匝数比为1:1)。

关于1.5kHz 振荡:我假设该 Cout 值(3000~5000uF)直接连接到 Vout、而不连接任何串联 R 或 L。为了防止此振荡、需要将哪些电阻(R)和电感(L)值与3000~5000uF 的 C 串联? 请分享计算(a) R 值(假设 L=0)和(b) L (假设 R=0)的公式、给定以下参数:

输出电压

2.输出电流(最大值)

3.C.

4. Vout 绕组(次级)与感测绕组的匝数比。

谢谢你。

此致、

卡洛

您好、Carlo、

本周、Uli 外出度假。 但是、以下链接中的 Webench 工具可用于根据输入和输出功率要求检查变压器匝数比设计、

此致、

Mike

您好、Carlo、

没有公式或公式可以描述或预测 Cout 过大时输出端可能出现的1.5kHz 纹波振荡。 这种情况 是一种观察到的现象,尚未经过数学分析。 早 在调查另一个问题时、就发现了5V 输出电压、只是非正式地描述了这一情况。 因此、我同意要避免的过量电容值将随输出电压和辅助绕组匝数比而变化。 但是、正如我之前提到的、这与客户的直接问题无关。

之前我曾建议过通过实验将 VS 电阻值减小10倍、以查看 VS 节点上的杂散电容是否可能是200mV、500Hz 振荡的源。 这会将任何时间常数延迟降至1/10。 客户是否能够执行此测试?

此外、请从 VS 节点上移除引线式探针电阻器。 客户使用该1~2K 电阻器将探针电容与 VS 隔离、但电阻器本身可以增加电容 和/或充当线天线 并将噪声注入 VS。

客户告知不管是否连接了探头、都有输出纹波。 如果引线式电阻器独立于示波器探针影响 VS 并保持就位、则可能会得出关于振荡源的错误结论。

我希望这个测试的结果是正的(即没有振荡)。

此致、

Ulrich

您好 Ulrich、

我收到了客户的以下更新:

关于使用示波器查看 VS (引脚6)的问题、我们在以下条件下对器件进行了全面测试:

在每种情况下、单元的行为都保持不变-不稳定的行为仍然存在。 因此、我们得出的结论是、我们探测 VS 引脚的方法对单元没有影响。

[引用 userid="64834" URL"~/support/power-management-group/power-management/f/power-management-forum/1003306/ucc28704-frequency-and-amplitude-modulation-modes/3731754 #3731754">之前、我曾建议将 VS 电阻值通过实验减小10倍、以查看 VS 节点上的杂散电容是否可能是200mV、500Hz 振荡的源。 这会将任何时间常数延迟降至1/10。 客户是否能够执行此测试?[/报价]我们理解这一拟议解决方案的动机,但是,我们没有沿着这条道路走下去,原因有两个:

我们决定不接受这个解决方案,因为它会导致该单元不符合有关线路电压启动和关断阈值的要求。 PCB 的布局已经是为了最大程度地减小杂散电容、如果不采用外来(&昂贵)材料、则无法进行改进。 如果这是一个"解决方案"、那么无论如何我们都需要选择一个新的 IC。

我们花时间探索其他解决方案-最终发现:一个22pF 电容器放置在 CS (引脚4)和 GND (引脚5)之间。 我还有其他与此解决方案相关的问题、我将在单独的帖子中提出这些问题。

请尽可能多地分享有关此问题的信息。 我们的应用可能与向您揭示此问题的情况非常相似、因为在我们的情况下、输出电容可能非常大。 在我们的应用中、该单元将通过通用+12V 总线在机架中提供多个 PCA 模块、并且每个 PCA 将其自己的滤波电容添加到该单元检测到的总电容中。 如果每个 PCA 都需要一些 R 或 L 系列以确保稳定性,则我们需要了解这一点,以便我们可以采取必要步骤,确保在安装了 PCA 卡的所有可能组合及其工作条件下的稳定性。

我们找到了一个解决方案:在 CS (引脚4)和 GND (引脚5)之间放置一个22pF 电容器。 无需进行其他更改。

这消除了所有不稳定行为。

但是、我现在还有其他与此解决方案相关的问题。

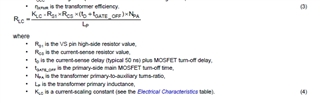

1. RLC (连接到 CS)是根据数据表 eqn 4 (或3?)计算得出的。 为2.2k (请参阅随附的屏幕截图)。 请确认使用的单位均为标准 SI 单位、例如:伏特、欧姆(非千欧)、秒(非毫微秒)、亨利(非微亨利)。

2.使 RLC 的价值(a)过低或(b)过高会产生什么后果?

感谢你的帮助。

此致、

卡洛

您好、Carlo、

我很高兴您的客户找到了不稳定问题的解决方案。 我不怀疑它与 CS 输入有某种关系、坦率地说、我不明白为什么会这样。 通常会在 CS 输入端添加一个小电容、以滤除前沿噪声尖峰、这些尖峰会提前超过电流感测阈值并关断栅极驱动器。 此类噪声(无 CCS)对运行的影响通常要比输出端的小纹波(但无法解释)严重得多。 但结果不言而喻。

要回答新问题:

公式(4)中用于计算 RLC 的单位均为标准 SI 单位。

2A。 RLC 过低意味着高压线路的 CS 失调电压不足 、与低压线路相比、高压线路的 Ippk 和输出电流(功率)更高。

2b. RLC 过高 意味 着高压线路上的 CS 失调电压过大 、导致 高压线路上的 Ippk 过低和输出电流(功率)低于低压线路。

恰好正确的 RLC 值将在 整个线路范围内产生恒定 IOCC 调节(在~5%以内)。

注意:引入 CCS 会添加另一个延迟项、以包含在等式(4)的 TD 中。 如果 RLC=2.2K 且 CCS=22pF、则添加48ns 的滤波器延时时间、这将影响 RLC 的理想值。 由于新的延时时间是 RLC 的函数、因此计算会 进行迭代以收敛于 RLC 的正确值。 由于额外的延迟 会增加 RLC、因此预计会有更高的 RC 时间常数加入到 TD 中。 通常、几次迭代应使您足够接近以保持良好的 IOCC 调节。 还可以在原型评估期间进行经验微调。

关于 Cout 值非常高的潜在不稳定性、我需要深入研究。 我会尽快回复。

此致、Ulrich