您好的支持团队。

我收到了客户关于 TPS56C215加电序列的一些问题。

1.在什么情况下纠正 VREG5的延迟时间为100us 或200us?

2. 如果200us 正确、为什么在将数据表从 Rev.C 更改为 D 时从 VREG5到 MODE 的读取开始延迟时间发生变化?

数据表 Rev.C 中的延迟时间为100us。

此致、

千兆

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Higa、

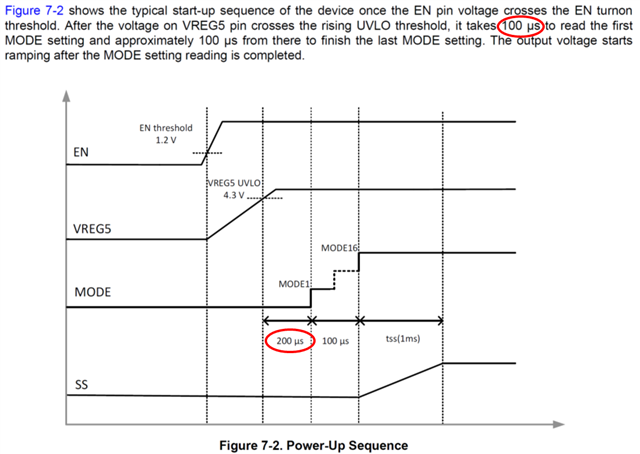

首先,延迟时间200us 应该是正确的。 应遗漏句子中的描述以进行更正。

从 Rev.C 更改为 Rev.D、图7-2不仅将延迟时间从100us 更改为200us、还将第四个信号从 Vout 更改为 SS、该信号与内部设计延迟相匹配。 图7-2加电序列不是工作台上的正确波形。 图7-2中的 MODE 信号只能显示用于检查 MODE 引脚分压比的内部模式基准电压。

总的来说、在 VREG5超过其 UVLO 后、到 SS 斜升的延迟时间应该大约为300us。

谢谢、

Lishuang