主题中讨论的其他器件: CSD17507Q5A、 CSD86336Q3D、 CSD86350Q5D、 CSD87351Q5D

您好!

我们计划在电路板中使用 TPS53015器件。 下面列出了我们的系统要求。

1.19V 输入(+/-5%)、3.3V 输出

输出电流:7A

工作温度:0°C 至50°C

2.19V 输入(+/-5%)、5V 输出

输出电流:6.5A

工作温度:0°C 至50°C

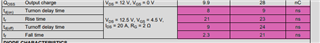

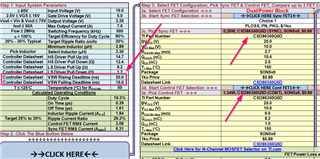

TPS53015数据表中的应用设计使用分立式 FET CSD17507Q5A 器件。 在 TI 的 FET 损耗计算表的帮助下、我们能够计算 FET 损耗、以确定使用和不使用外部栅极电阻器时的最高环境温度(仅适用于 HS FET)。 我们已将所附工作表中的值列出为一个列表(请参阅" FET 损耗(分立式)"工作表)。 我们还根据 FET 损耗计算表、并将损耗和最高环境温度值以列表形式列出(请参阅" FET 损耗(双通道)"表)、考虑了半桥 FET 器件(CSD86336Q3D、CSD86350Q5D)。

根据 CSD17507Q5A 数据表、RJA 值取决于连接漏极焊盘的铜面积。 数据表建议、对于最小漏极焊盘面积、RJA 应为125C/W 尽管连接控制 FET 漏极的 VIN 布线可能具有更大的覆铜面积、但根据我们对其 SW 节点的理解、连接同步 FET 漏极的覆铜面积需要尽可能小。

Q1)在这种情况下、我们无法满足产品的环境温度要求50°C。 您能否告诉我们、是否有办法克服这一问题以使用分立式 FET?

从 FET 损耗表中确定的双 FET 器件似乎具有 PGND 焊盘、可将 PGND 焊盘连接到 GND 以使热量从 FET 排出。 我们的设计至少具有2个 GND 平面、我们认为这应该有助于降低 RJA 值。

Q2)您能否告诉我们、我们是否可以将建议的双 FET 器件与 TPS53015 (0°C 至50°C)配合使用?

FET 损耗值至少增加了~0.3W、并在 HS FET 中添加了10 Ω 栅极电阻器。 该应用设计仅包含相同的 HS FET、而不包括 LS FET。 额外的损耗使计算得出的最高环境温度降至50C。 (注意:在 TPS53015的最大 HS 驱动器上拉/下拉值的基础上添加了10欧姆、以计算损耗)

Q3)是否可以将栅极电阻器替换为零欧姆? 此外、我们是否还需要包含一个用于 LS FET 栅极的电源?

我们还附上了用于损耗计算的 TI FET 表。 如果您对这些值有任何了解、请告知我们。

我们期待您尽早回复、因为我们处于设计阶段。

谢谢、

Balaji