您好专家、

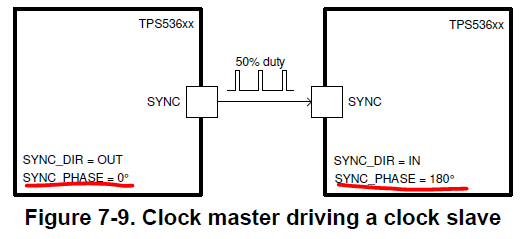

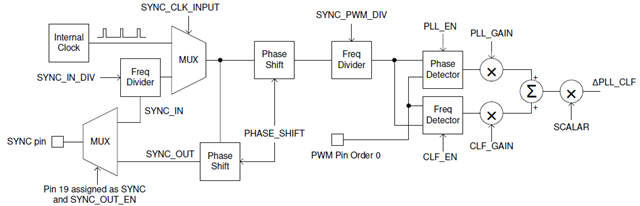

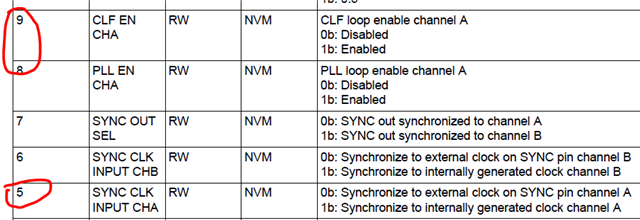

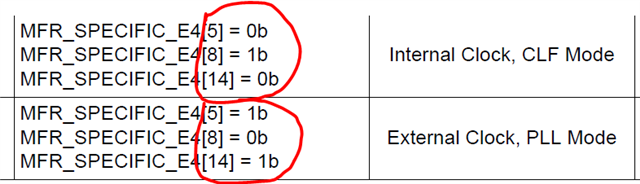

此器件具有 SYNC 引脚并具有同步模式选项:CLF 模式(内部 CLK)和 PLL 模式(外部 CLK)。 它可通过 E4h 进行配置。

我的问题:

1.以下从两个地方(DS、TRM)发现的这些情况为什么不同? 在 DS 中、这两种模式中只有一种模式可以实现。

但在 TRM 中、这两个使能信号是独立的。 CLF 环路和 PLL 环路能否同时运行? 此外、E4h[14]看起来与启用的模式没有关系。

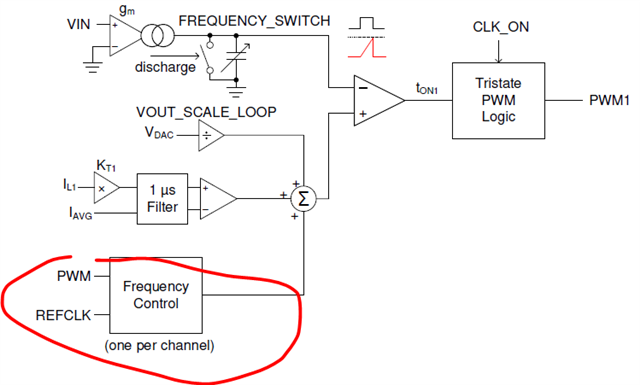

2. CLF 环路是一个缓慢的闭环频率环路、用于调整导通时间、以确保 FSW 接近我们设置的目标 Fsw、尤其是在负载电流较高时。

然而、频率控制在每个通道上声明一个、例如、通道 A 配置为总共12 pH。 这是否意味着第1相-第12相将共享相同的频率控制输出 Δton μ s、并且仅与 PWM 阶数0一同使用?

PLL 环路仅用于特定 CLK 的相位跟踪、这意味着我们可以使用两个 TPS536C7实现24ph 交错、对吧?