您好、管理员、

我对将 TPS548B22用于 Xilinx FPGA 有疑问。

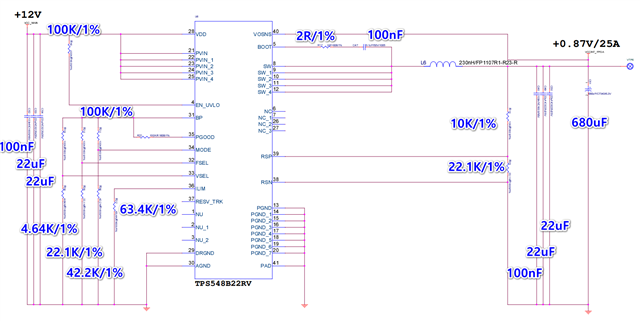

Web 工作台设置如下所示。

-输入:12-14V

输出:0.87V

-输出电流:25A

输出电路图不同于 Web 工作台输出、它始终输出0.43V。

我们的电路有什么问题?

对于 Web 工作台、所有事情都必须相同、例如输入和输出电容器以及任何电阻器?

2.如何更改原理图以获得更好的性能和0.87V 的稳定输出?

等待您的善意回复

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、管理员、

我对将 TPS548B22用于 Xilinx FPGA 有疑问。

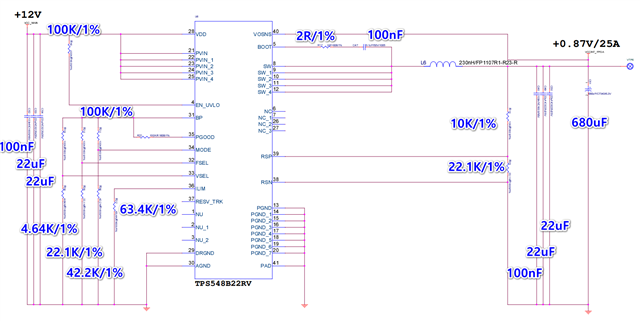

Web 工作台设置如下所示。

-输入:12-14V

输出:0.87V

-输出电流:25A

输出电路图不同于 Web 工作台输出、它始终输出0.43V。

我们的电路有什么问题?

对于 Web 工作台、所有事情都必须相同、例如输入和输出电容器以及任何电阻器?

2.如何更改原理图以获得更好的性能和0.87V 的稳定输出?

等待您的善意回复

谢谢。

您好!

要回答您的问题:

如果您具有足够的输入/输出电容、则该电路无需与 WebBench 输出相匹配、并遵循数据表中详述的指南。 就输出电压而言、0.43V 小于器件的最小基准电压、这种情况不应发生。 您的基准电压设置为0.5995V、从 Vout 到 RSP/RSN 的电阻分压器似乎是实现0.87V 输出电压的正确比率。 通过查看开关频率选择、您似乎有足够的裕度来避免最小导通时间控制器限制。 您是否有任何数据(例如 SW 节点波形)可以更好地了解为何未实现稳压? 正如您在注释中提到的、EN 引脚确实需要一个分压器、因为12-14V 确实违反了 EN/UVLO 的最大引脚电压额定值。

2.就性能而言,原理图显示的电压为0.87V。 您是否必须对设计进行优化的参数、例如瞬态响应或纹波?

Alec Biesterfeld

BSR-MV-应用