你(们)好

我正在寻找一个组件、 TPS54J061非常适合我的设计、但放电功能会影响其他功率损耗保护功能。

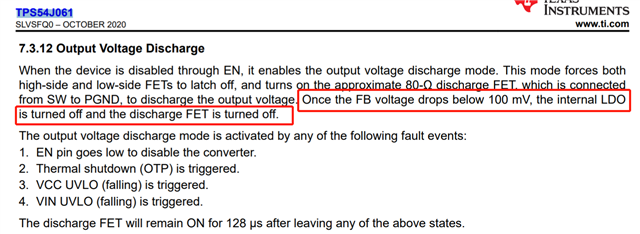

但我看到、在 VFB 低于100mV 后、放电将在内部被禁用。 我想知道、在 EN 为低电平后、是否可以强制将 VFB 拉至 GND 以禁用放电功能?

谢谢。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的 Ni:

这应该是可能的,但需要认真地做。 将元件连接到 FB 引脚可能会影响稳定性或导致 FB 引脚上拾取噪声。 为了防止它引起问题、用于下拉 FB 的放电路径可能需要相对较高的电阻、而不是如所需的那样有效。

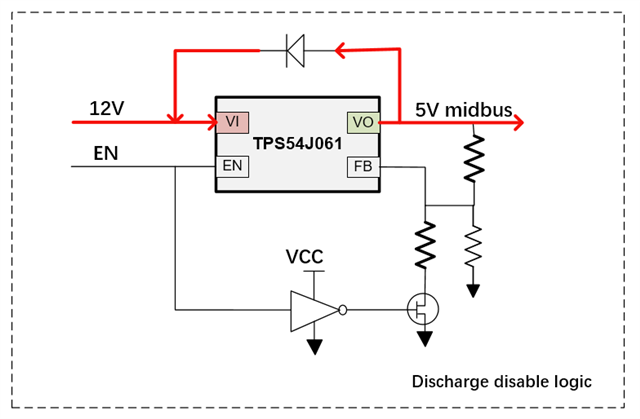

例如、您可能可以使用 N FET 来下拉 FB 引脚。 我建议在 N FET 的漏极和 FB 引脚之间放置一个电阻器。 这将最大限度地减少从这个外部电路拾取的噪声和 N FET 电容的影响。

在该应用中、您似乎希望在禁用 TPS54J061时尽可能长地保持输出高电平。 您能否详细介绍一下为什么需要这种解决方案? 它似乎不会节省这么多的能量。 是否有另一个电源电路连接到 TSP54J061的输出端?

Anthony

你好、Anthony

感谢您的回复。

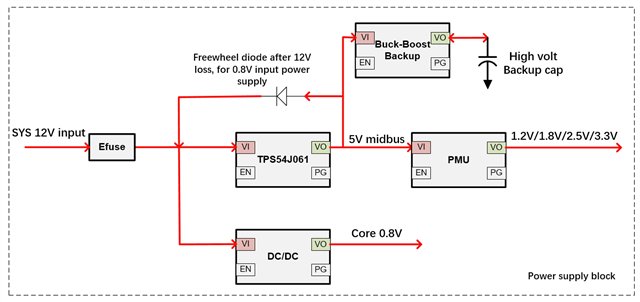

是的、输入电压损失后存在功率损耗备用机制。 "电源块"是电源的演示。

在正常运行中、5V 中总线是许多次级直流/直流转换器的输入、也是备用电容器充电电路的输入。 在功率损耗期间、TPS54J061将被 MCU 自动禁用、备用电容器将在降压模式下工作、并将电容器能量转换为5V、以在 整个器件上持续几秒钟。

因此、我需要在备份阶段将 TPS54J061置于高阻抗状态。 放电功能将导致能量泄漏。

根据您的建议、请参阅"放电禁用逻辑"。 我有一些问题需要您帮助确认:

在上电序列期间、TPS54J061的使能必须早于 NOR GATE 的"VCC"、以确保在 TPS54J061软启动期间不会出现上电干扰或不必要的 FB 拉至低电平。 对吗?

在 断电/断电序列后、TPS54J061将禁用、EN 必须保持低电平、VCC 必须在整个电容器备份级期间保持有效电压。 对吗?

3、即使 FB 被拉低、实际上 TPS54J061的 VIN 和 Vout (SW 节点)在电容备份级期间仍保持在5V 电压、因为没有电路 对其进行隔离。 TPS54J061是否安全? 我担心 TPS54J061受到 EOS 损坏

任何其他建议、请告诉我。

谢谢。

感谢您提供更多详细信息。 这是有道理的。 总的来说、您需要确保在启用 TPS54J061之前关闭用于下拉 FB 的 FET、并且您需要确保在 FET 打开之前禁用 TPS54J061。

为了完成上述操作、如果逆变器的 VCC 在 EN 引脚之前、应该是可以的。 一旦 EN 引脚变为高电平、逆变器的输出将在 TPS54J061开始切换之前很快变为低电平。 在 TPS54J061开始切换之前、需要~400µs μ s 来检测和设置模式设置。 我想此逆变器的延迟要低得多、并且其输出将稳定至低电平状态。

是的、为了使下拉 FET 保持导通状态、您需要在电容器备份阶段使 VCC 保持活动状态。

TPS54J061在禁用时可将 VIN 和 VOUT 保持在5V、这是没有问题的。 唯一的问题是、是否可能有大量的无限电流从 VOUT 流回 VIN、流经 HS FET 的体二极管。 您添加的外部二极管与 HS FET 的体二极管并联、如果不是所有用于为0.8V 稳压器供电的电流、则应传导大部分电流。

您能否分享您想用于 FB 分压器和下拉 FET 漏极的电阻器值?