请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

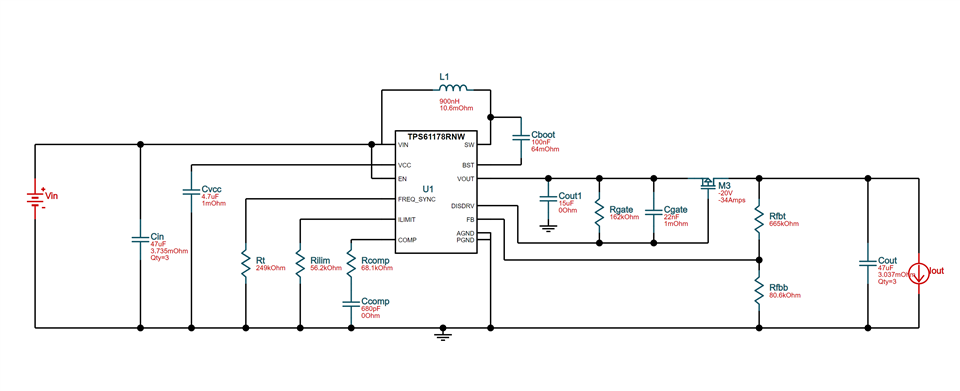

器件型号:TPS61178 主题中讨论的其他器件: CSD25404Q3

大家好、all...please 帮我消除疲劳、但在我看来 、TPS61178RNWR 的数据表可能有错误...?

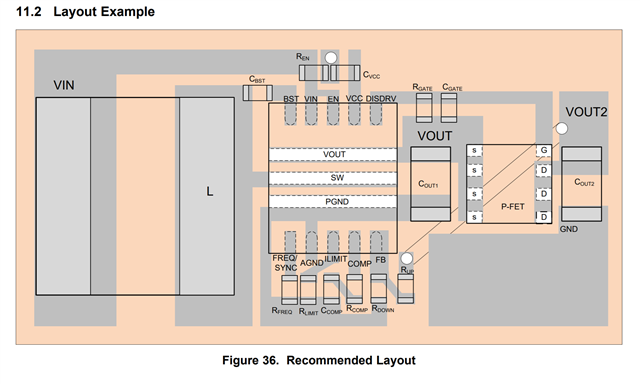

11.2布局示例

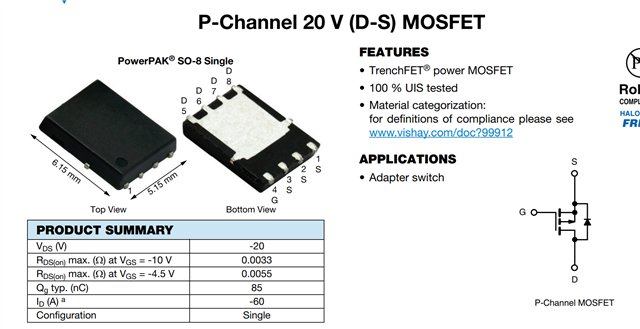

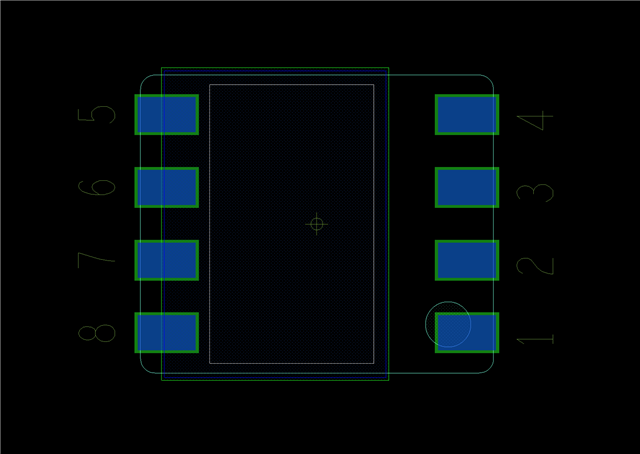

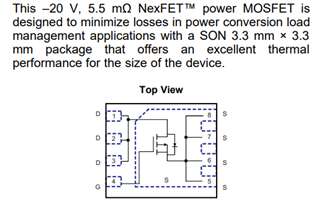

FET 是一个 P 通道、器 件型号:每个 webench 的 Si7633DP、但在我看来、S 和 D 在布局图中是向后的。

你说什么?

https://www.vishay.com/docs/69008/si7633dp.pdf