主题中讨论的其他器件:UCC12040、 UCC12051-Q1、

您好!

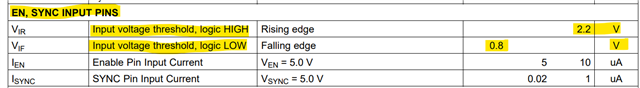

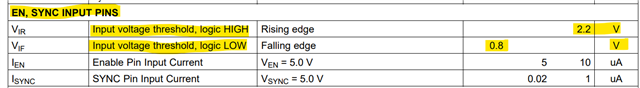

我们要检查同步输入引脚是否可以使用外部3.3V 时钟信号驱动、根据数据表、这似乎是可行的。

请确认吗?

此致、

Minkyun

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们要检查同步输入引脚是否可以使用外部3.3V 时钟信号驱动、根据数据表、这似乎是可行的。

请确认吗?

此致、

Minkyun

Minkyun、

感谢您通过 E2E 进行连接。 如您所示、UCC12040、UCC12050、UCC12051-Q1 SYNC 引脚具有 TTL 兼容型阈值。 应用一个3.3V SYNC 信号是合适的。 请注意 UCC12050数据表中的第7.3.5节。 应用的 SYNC 信号必须为16MHz ±10%、并且当应用外部 SYNC 信号时、内部展频调制(SSM)将被禁用。 如果没有启用 SSM、峰值 EMI 将会更高。 根据您的建议、希望在外部驱动 SYNC 引脚的客户通常使用具有自己 SSM (频率抖动)功能的数字时钟信号、或者他们希望将基本频率稍微偏离16MHz。 您在外部驱动 SYNC 引脚的目标是什么?

我支持使用此器件的应用、您可以直接通过 s-mappus@ti.com 与我联系

此致、

Steve M

您好 Steven、

感谢您的快速回答。 我们计划使用十二(x12)个 UCC12050来创建彼此隔离的浮动5V 电源。 它们中的每一个都将提供一个半桥电源模块。 为了避免拍频问题、我们想要同步所有12个 ISO dc/dc (按照数据表说明)。 我们为此特定功能选择了 UCC12050。

但我们不知道外部时钟信号应该(或建议)实施扩频调制。 由于开关频率为16MHz/2 = 8MHz、因此我们认为 与其他系统的开关频率相比、这足够高。 例如、半桥开关频率约为40kHz。

此外、该系统适用于实验室级电机驱动。 因此、我们没有过多地考虑 EMI 法规。 当我们忽略 SYNC 信号的 SSM 时、您能更详细地解释一些风险或问题吗?

顺便说一下、我们计划从 FPGA 模块生成同步信号。

感谢你的帮助、

Minkyun

Minkyun、

如果您不关心 EMI、那么您也不应该关心"拍频"、因此、根据您描述的用例、我建议不要将它们同步在一起、或者至少允许任一/或选项应用 SYNC 或不应用 SYNC。 您将测量同步与非同步情况之间 VISO 纹波的轻微差异。 将16MHz 时钟扇出到12个使用点可能会在 PCB 中引入其他问题、因此请注意 PCB 布局-希望您能够以足够好的完整性传输这些信号、以便在每个 UCC12050处进行同步。 祝你好运。

此致、

Steve M