您好!

我正在进行产品重新设计、并将 TLC5928DBQ 驱动器集成到电路板上以替代替代替代解决方案。

原型运行正常、但我注意到在进行了 sch/布局之后、SIN/SOT/CLK 时序可能"危险"。

实际上、SIN 采样阶段在 CLK 的上升沿完成、但 Sout 也在 CLK 边沿上更新(延迟很小)。

我在 LED 面板上连接了16个驱动器、长度约为30cm。 所有器件共享相同的 CLK、LD 和 OE 信号。 因此、假设源阻抗相同、CLK 的上升时间将比 Sout 上升时间长、这是因为每个 Sout 在16个输入上分离 CLK 信号、而不是仅在1个栅极上分离。

如果某些驱动器具有不同的 CLK VIH 电平(生产容差或与温度相关的容差)、如果 VIH (DRIVER#n)< VIH (DRIVER#n+1)、则有可能在 SIN 的采样阶段开始之前更新驱动器#N 的 Sout 信号。

我尝试提高 CLK 的电压速率以获得最快的信号上升时间、但这在具有较长布线长度的电路板上非常复杂、我会遇到过冲和反射问题、还会引入我希望避免的 EMC 问题。

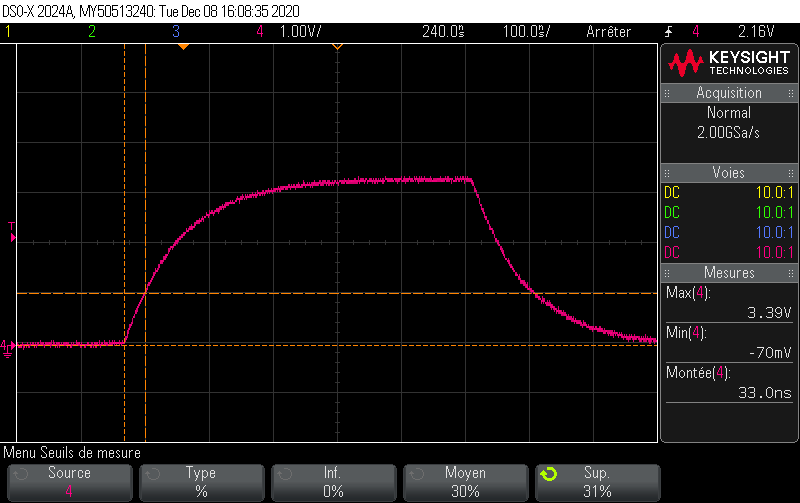

我有一个想法并在一个驱动器上对其进行了测试、但我需要获得您对此的反馈。 我的解决方案是在任何 Sout 到 SIN 连接之间放置一个 RC 网络(2.5K+22pF、因为这些值已经出现在我的电路板上)。 这将降低 SIN 输入端检测到的 Sout 信号的上升速率、从而确保始终在正确的 Sout 值上执行 SIN 采样阶段。 (CLK 速度约为1MHz)。 任何其他信号(CLK、LD、OE)都有一个47欧姆的串行电阻器、用于降低信号上升速率、然后降低 EMC。

但是、即使这适用于一个驱动器、我也需要确认用于我们生产的解决方案(大约300K 驱动器...)。 我唯一的问题是输入拓扑能适应如此长的上升速率:它们是否都在施密特触发器中? 在数据表的引脚排列表中、只有 CLK 信号被标记为施密特触发器、但没有其他引脚的指示;但是、在内部图中、所有输入上都显示了施密特触发器图片。 这对于实现完全的生产可靠性非常重要。

谢谢你

Aurelien