您好!

我有两个采用菊花链配置的 TLC59581芯片。 时钟和数据信号由 FPGA 构成。 SCLK 频率为2MHz、GCLK 为4MHz、SIN 线路上的数据在 SCLK 上升前的150ns 前被设置。

我可以将 GS 数据正确移入两个 TLC59581芯片的存储器组中。 使用以下序列:

- 移位链中第二个芯片的48位 GS 数据以及48个 SCLK 脉冲

- 移动第一个芯片的另外48位 GS 数据、以及另外48个 SCLK 脉冲

- 将 LAT 置为有效并发出1个 SCLK 脉冲、然后将 LAT 置为无效-这会发出 WRTGS 命令

- 重复上述步骤15次、以填充一行存储器组

- 重复 N 次以填充更多存储器组行

- 将 LAT 置为有效并发出3个 SCLK 脉冲、然后将 LAT 置为无效-这将使 VSYNC 命令生效

持续提供 GCLK。 在 VSYNC 命令之后、两个 TLC59581根据发送的 GS 数据模式驱动其 LED、这使我认为正在正确访问 TLC59581芯片内的48位通用移位寄存器。

但是、我似乎无法写入 FC1和 FC2寄存器。 使用的过程与 GS 数据模式传输几乎相似:

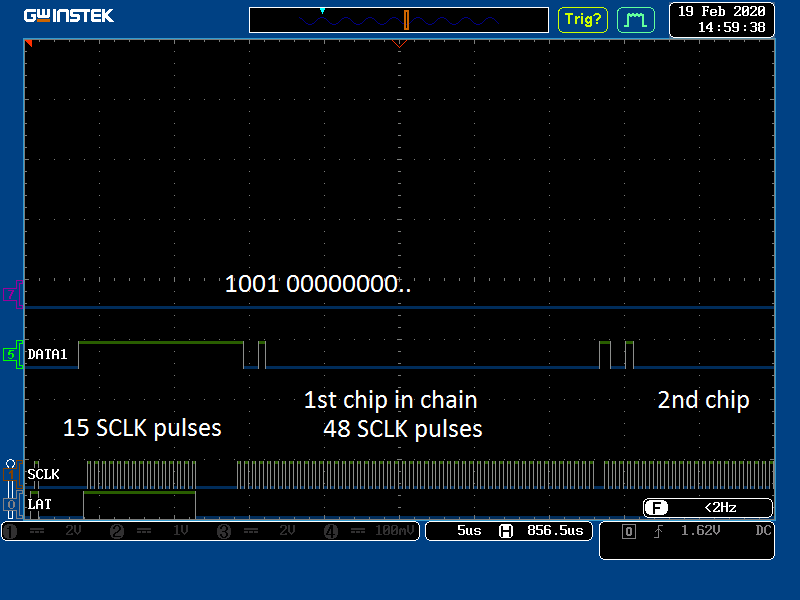

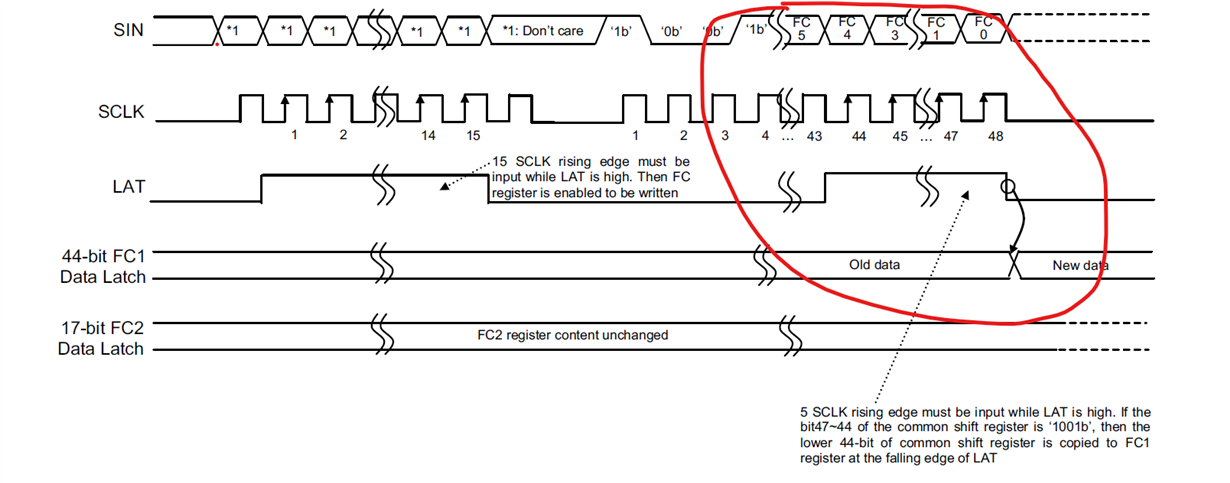

- 将 LAT 置为有效并发出15个 SCLK 脉冲、然后将 LAT 置为无效-这将发出 FCWRTEN 命令

- 移位48位 FC 数据、前4位对于 FC1为"1001"、对于 FC2为"0110"、以及48个 SCLK 脉冲

- 将 LAT 置为有效并发出5个 SCLK 脉冲、然后将 LAT 置为无效-这会发出 WRTFC 命令

编辑。 我附加了 FCWRTEN 的捕捉、然后是所有零的 WRTFC1。

目前无法读回 FC1和 FC2内容、因此我将使用 FC1和 FC2值来改变 LED 的亮度和扫描模式。 例如、发送的 FC1值除'1001'位47-44之外均为零、我希望将 BC 和 CCR、CCG、CCB 降至零、从而有效地消隐显示屏。 但这种情况并未发生。

我还对 FC2寄存器的位数据说为44 (43..0)稍微感到困惑、请参阅表7。 SLVA744数据表中的 FC2寄存器位分配、日期为2016年1月。 图6显示的情况不会亮起。 通用移位寄存器和数据锁存配置、其中提到了从通用移位寄存器锁存到 FC2的17位、以及 表3。 WRTFC/FCWRTEN 命令说明、其中还提到17位:

"如果‘公共移位寄存器第47–44位接收到0110b’,则公共移位寄存器中的低17位将被复制到 FC2寄存器中"

期待收到任何意见和建议。

此致、

Tim