Other Parts Discussed in Thread: TPS7A8300, TPS7A83A

主题中讨论的其他器件: TPS7A83A

你好

TPS7A8300是我们最喜欢的 LDO 之一、因为它集良好的 PSRR、低噪声和小压降电压以及小型封装和良好的热性能于一体。

但是、最近我们看到客户对非常小的产品的需求增加、尤其是在高度。 这导致了我关于 LDO 输出电容器选择的问题:

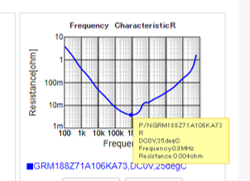

数据表建议至少使用22uF 陶瓷电容器。 我发现的最短22uF 电容器为1.6mm。 我需要最大为1mm 的电容器 因此、我想并行使用2或3个 GRM188Z71A106KA73D。 输出电压通常为3.3、1.8、1.2、0.9V (主要用于为 TI DAC 供电)

注意:由于温度原因。 我们仅使用 X7R 或更高类型。

您能不能就这些输出电容器的 LDO 性能提出建议? 足够2还是需要3个? 您可以对此进行仿真吗?

谢谢