请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC21222-Q1 大家好、

我可以看到为0负载电容提供了传播延迟(最小28ns 和最大40ns)。

我尝试在安装 MOSFET 的情况下测量相同的值。

我们是否有一条传播延迟与负载电容间的关系曲线。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我可以看到为0负载电容提供了传播延迟(最小28ns 和最大40ns)。

我尝试在安装 MOSFET 的情况下测量相同的值。

我们是否有一条传播延迟与负载电容间的关系曲线。

Mohana、

感谢您的提问。

正确的是、此参数未在数据表中指定、仅适用于0pF 负载。

我们可以使用 PSPICE 模型来估算或仿真负载电容上的延迟。

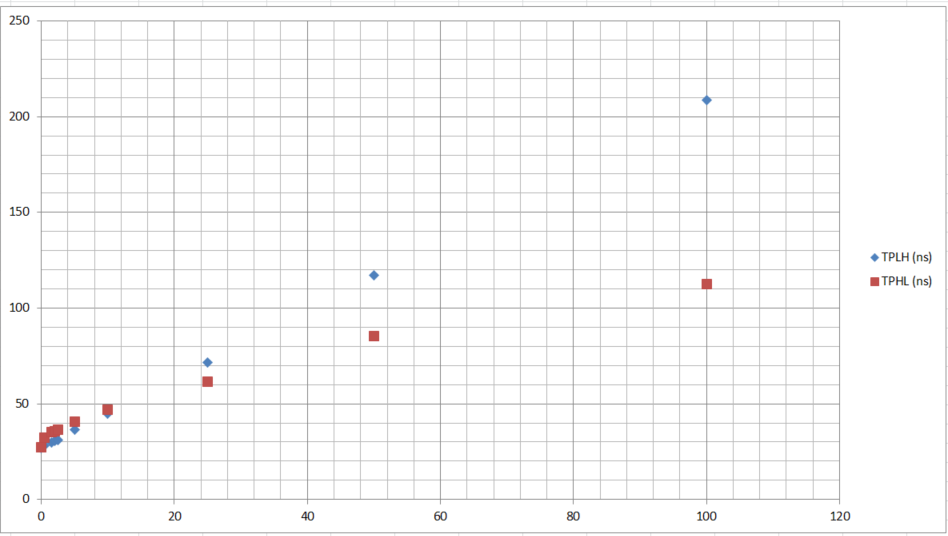

例如、我使用作为 UCC21222-Q1 PSPICE 模型一部分提供的示例项目、在多个负载电容下模拟了传播延迟、最高可达到极高的值。 结果如下、以及我们提供的设计文件的快照。 请注意、这是在固定温度下使用的典型模型、应用于估算。

希望这对您有所帮助。 如果这回答了您的问题、请单击绿色按钮让我知道。 如果您有任何其他问题、请告知我们。

最好

Dimitri