您好!

我正在使用 LM3481设计升压转换器。 当升压转换器关闭时、我希望系统尽可能处于最低功耗状态。

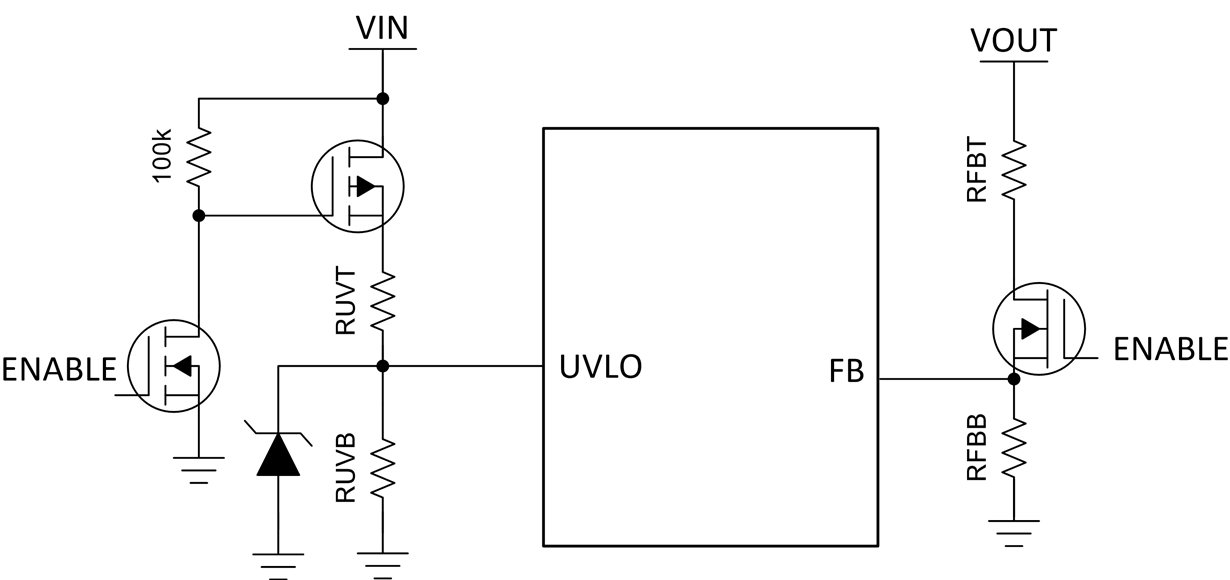

有两个接地的电阻路径:

- 反馈网络的电阻分压器

- UVLO 接地路径(具有额外的齐纳二极管、可防止该引脚电压超过6V)

如何降低这两条路径的电流消耗?

在之前的一个请求中、我要求提供可用于反馈网络的最大电阻器、并被告知底部电阻器应小于100k。 对于我的应用(升压至12V)、这将提供 Ra = 845k、Rb = 100k 的反馈网络。 当升压至12V 时、这会将电流限制为~12.7uA。 是否有办法进一步减少这种情况? 我考虑在 RB 和接地之间添加一个 NMOS、并将栅极连接到我的 Boost_en 信号、但当 FET 关断时、FB 引脚将经历>6V (尽管这将通过 Ra)。 如果我使用 FET 来有效地禁用反馈网络、这是否会成为一个问题?

对于 UVLO 接地电阻路径、我可以在这里使用什么最大电阻值来限制电流消耗? 由于我的 VIN 大于6V、我还需要添加一个齐纳二极管来限制 UVLO 引脚电压(这将消耗额外的电流)。 我不需要使用 UVLO 功能、是否有办法在不需要接地电阻路径的情况下有效地禁用此功能?

非常感谢您提供的任何帮助。

谢谢、

Andrew