主题中讨论的其他器件: ISO7760

您好!

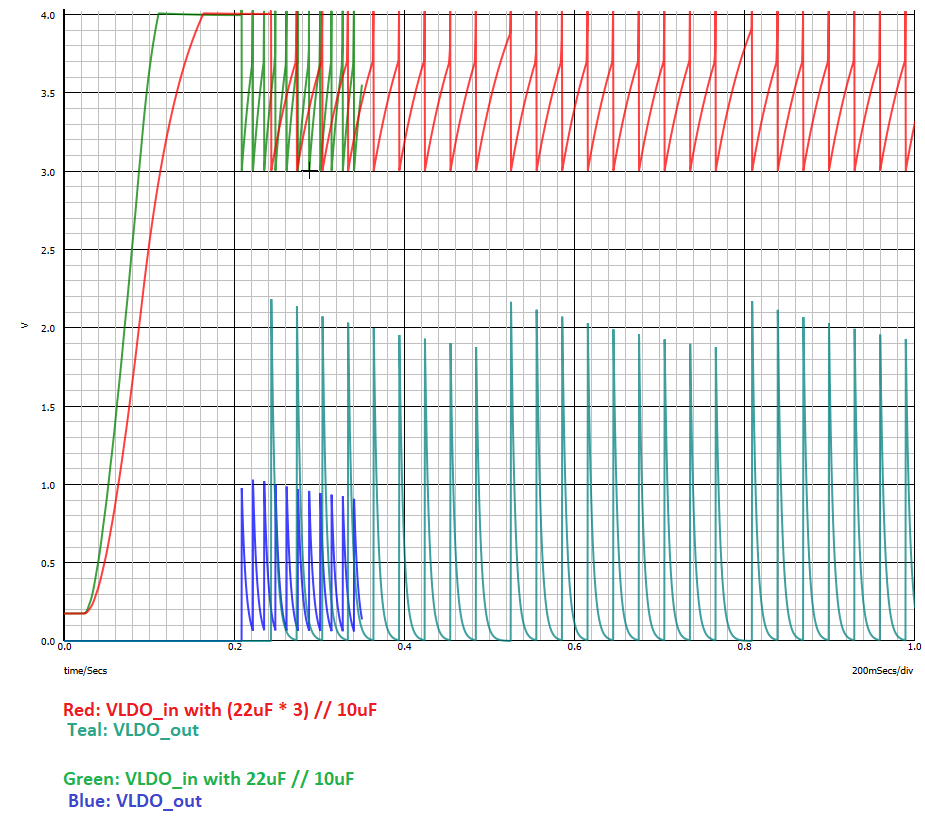

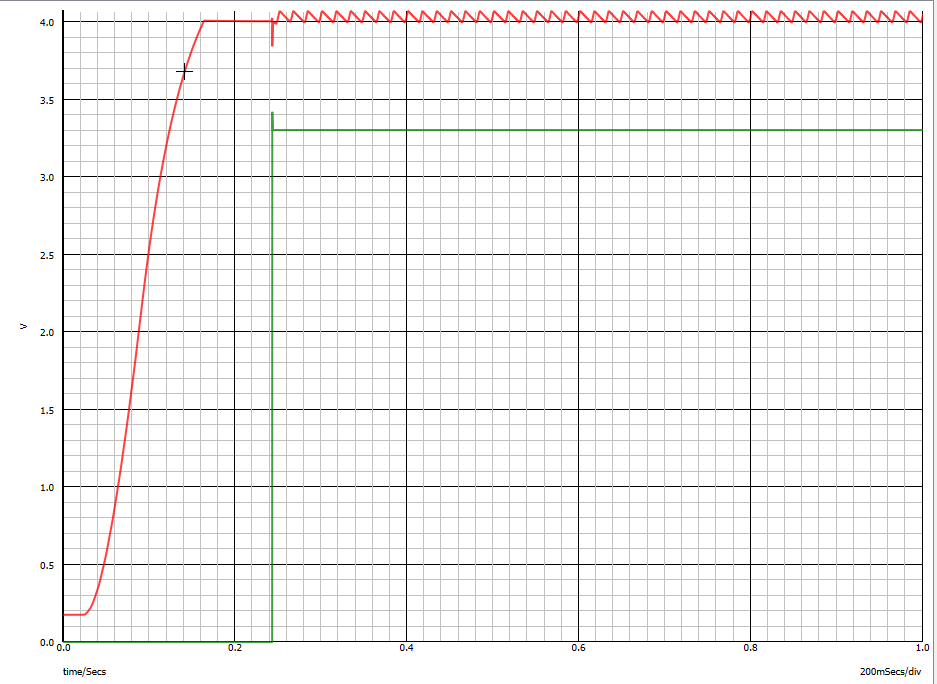

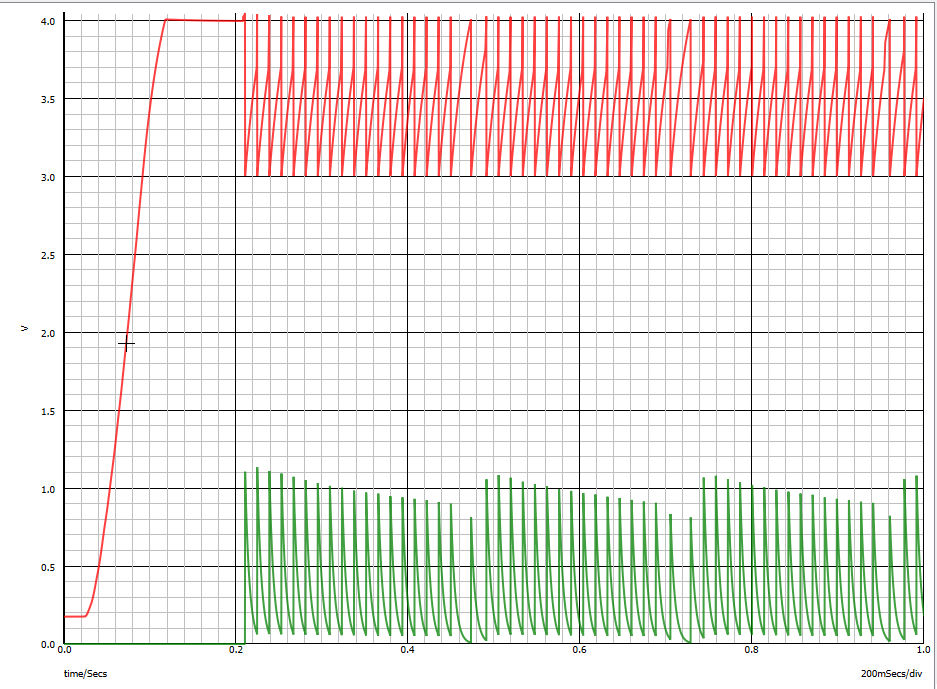

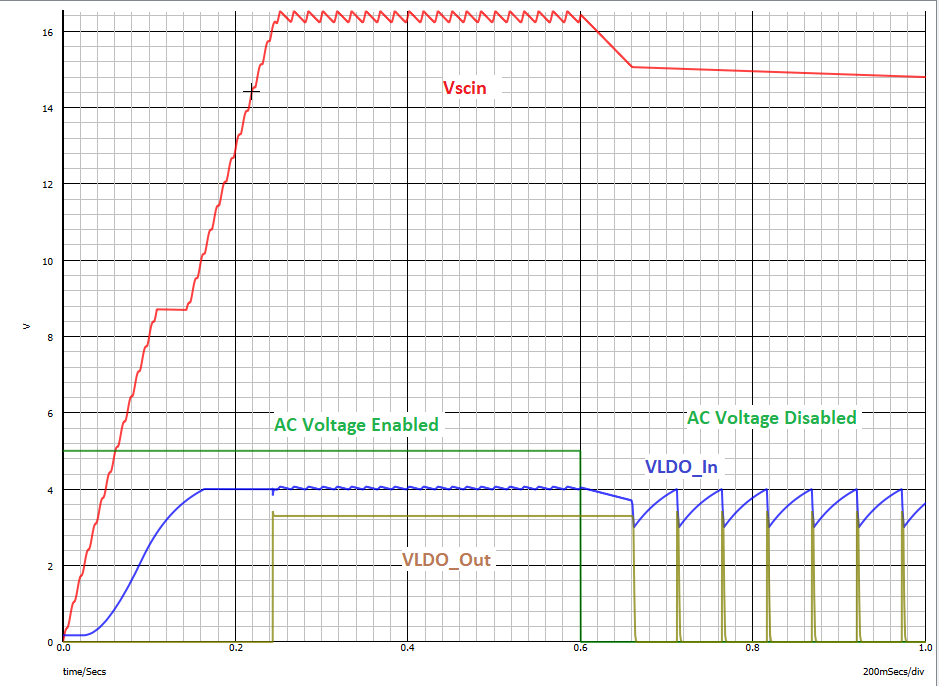

我有一个在 HB 模式下使用 TPS7A7833PWPT 的设计。 它间歇性上电、LDO_OUT 为1.7V、而不是3.3V。 我怀疑这可能与我违反 Cldo 输入/ Cldo 输出10:1比率有关。 我的电路值如下:

TPS7A78处于 HB 模式

CS:680nF

RS:330R

Cscin:330uF + 100nF

Csc1:1U +100N

Csc2:2.2u + 100N

Cldo_in:22U+10U

Cldo_out:22U+22u+1U+100N

如果你能...

1. 解释 LDO_OUT 上的间歇1.7V。

2.解释10:1比率要求

如何计算 TPS7A78在 HB 模式下的保持时间。 我假设断电时 TPS7A78仍由 Cscin 供电?

谢谢

TC