请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM27402 大家好、

使用 LM27402时、我有2个问题。

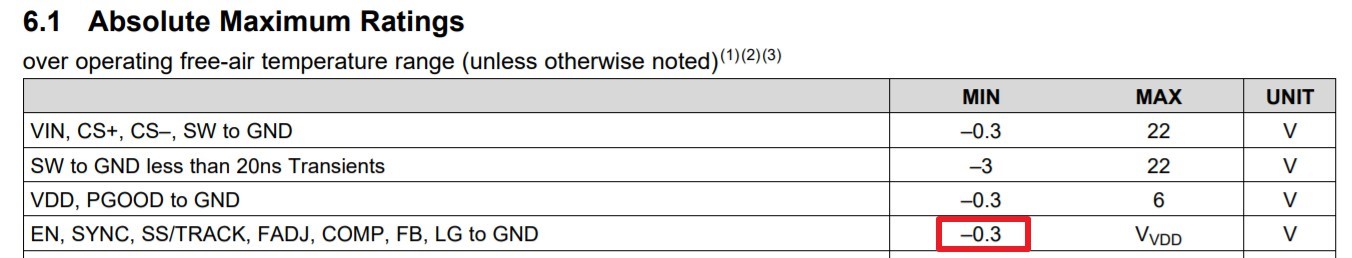

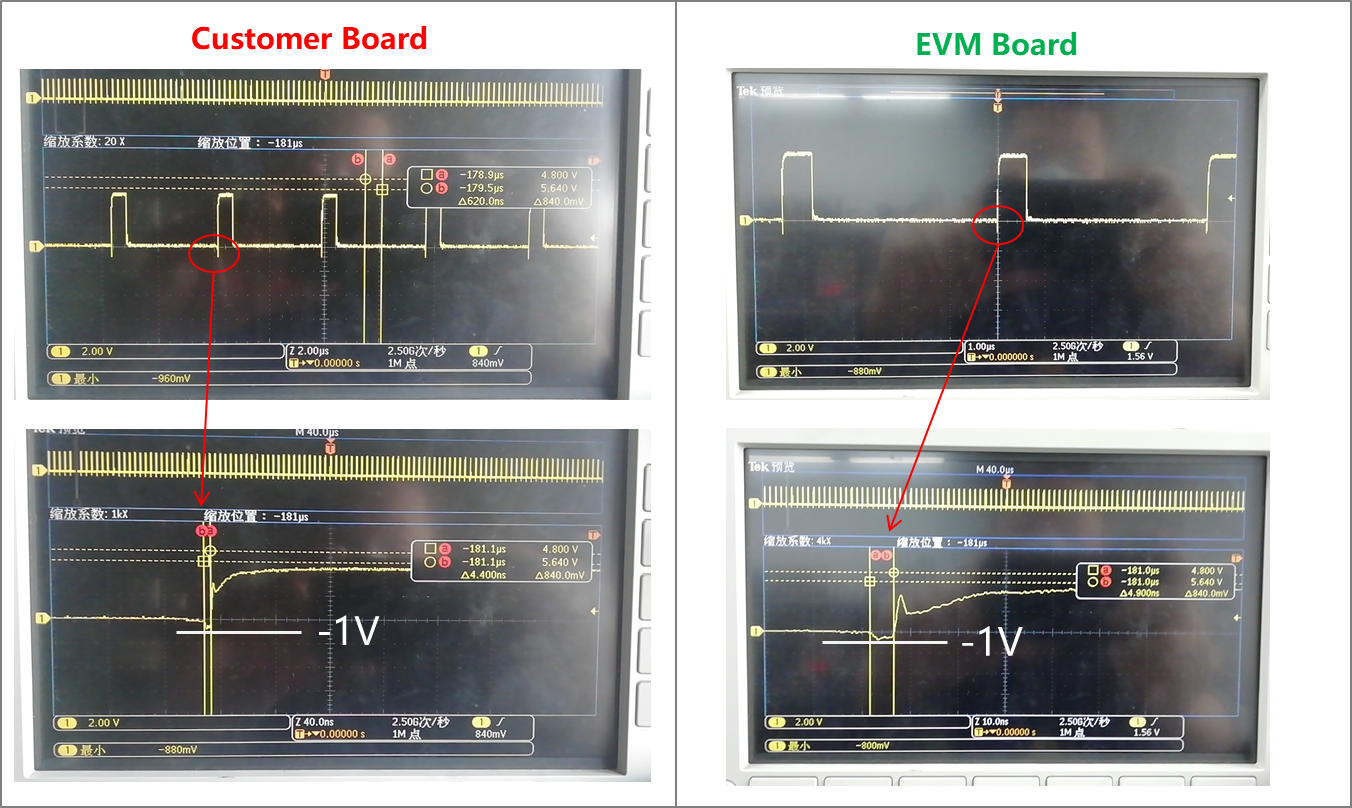

Q1:数据表显示 LG 上的最小电压不能超过-0.3V、而客户电路板和 EVM 在开启低侧 FET 时均显示大约-1V (周期4ns)、如下所示。

显然、它超出了数据表规格。 您能否帮助解释为什么它在开启时开始下冲至-1V? 由于 EVM 也存在这种现象、它是否正常? 如果它可能具有负过冲、那么允许的最大时间是多少?

Q2: HG 的绝对最大额定值是多少? 数据表中未显示该值。

非常感谢。

此致、

杨