主题中讨论的其他器件: UCC21732、

大家好、

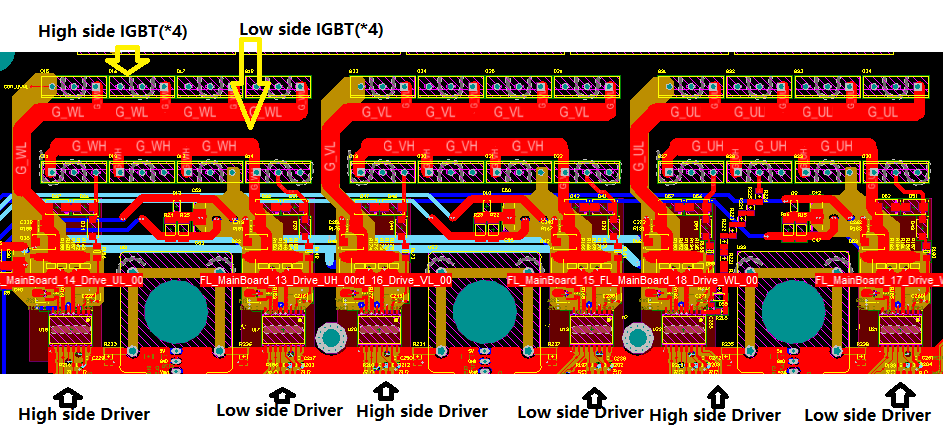

UCC21750也用于客户牵引逆变器、存在一些问题。 请就此提供帮助。 谢谢。

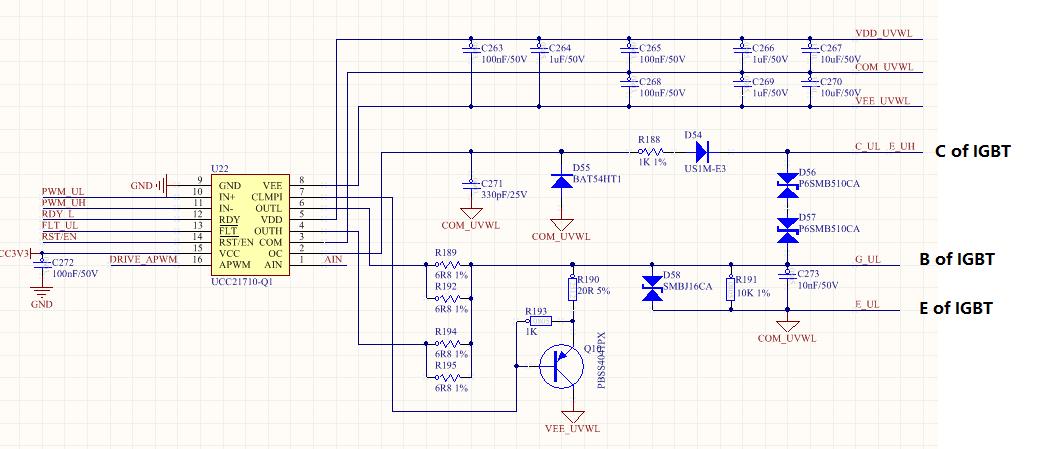

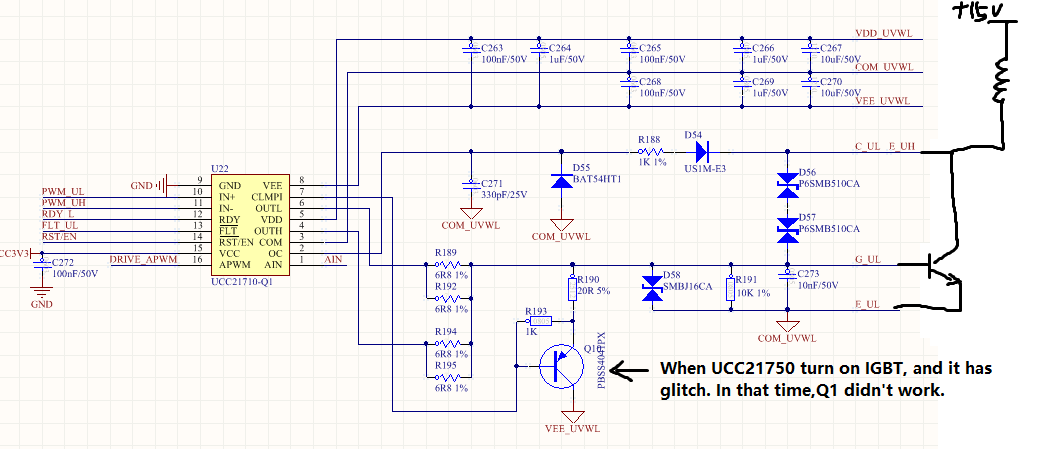

以下是客户提供的原理图:

测试条件:

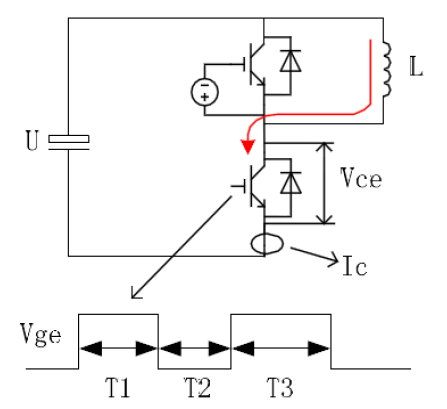

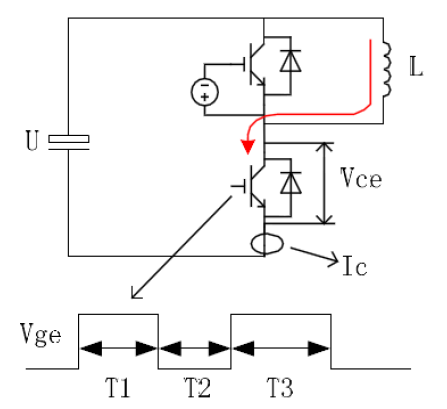

在高侧 IGBT 上并联了一个外部电感器、如图1所示;

问题:

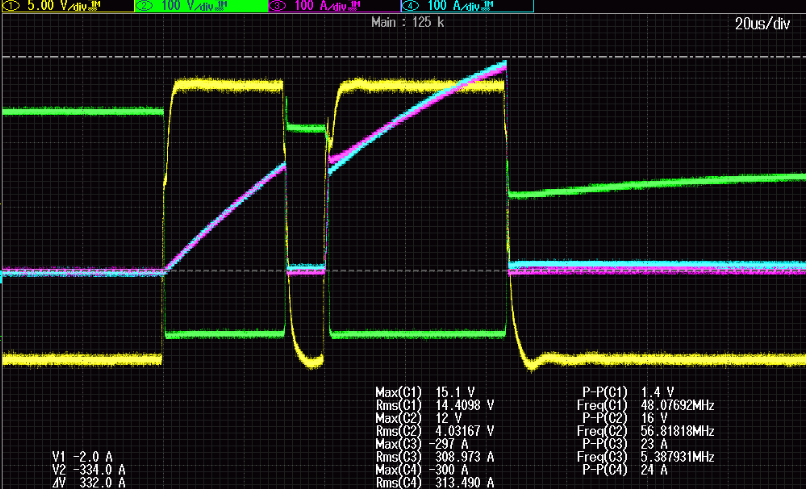

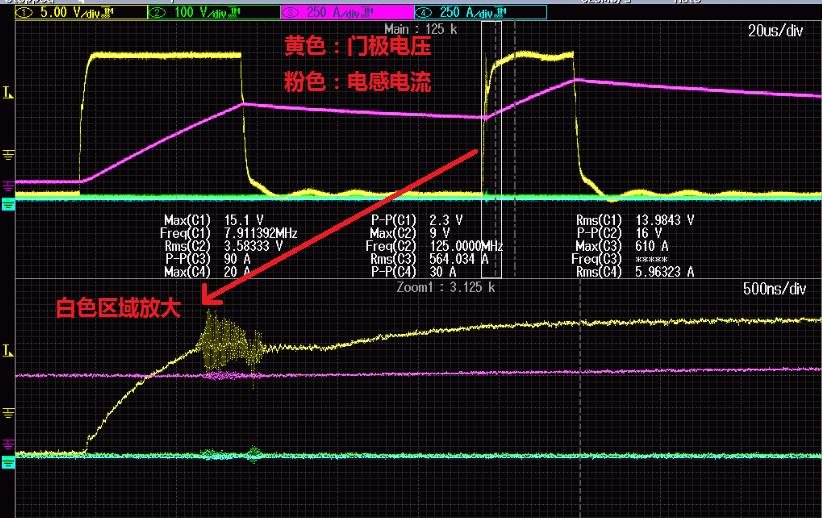

当客户使用触发波形来驱动 IGBT 时、它第一次在 T1和 T3中运行良好、如图2所示;

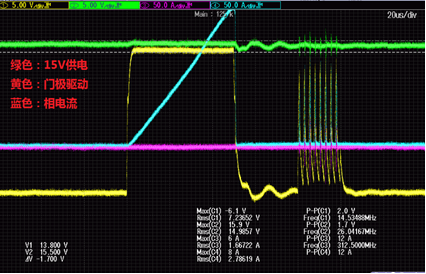

但是、当客户使用相同的波形第二次触发 IGBT 时、OUTH (引脚4)中会出现很多毛刺脉冲。 如图3所示。

图1测试条件

图2 (OUTH 为黄色、OC 为绿色(PIN2)、IGBT 中的电流为粉色和蓝色)

图3 (OUTH 为黄色、OC 为绿色、IGBT 为15V 时为绿色、IGBT 中的电流为蓝色)

有关 IGBT 的信息

e2e.ti.com/.../FGY160T65SPD_5F00_F085.PDF

BR

郭松珍