大家好、

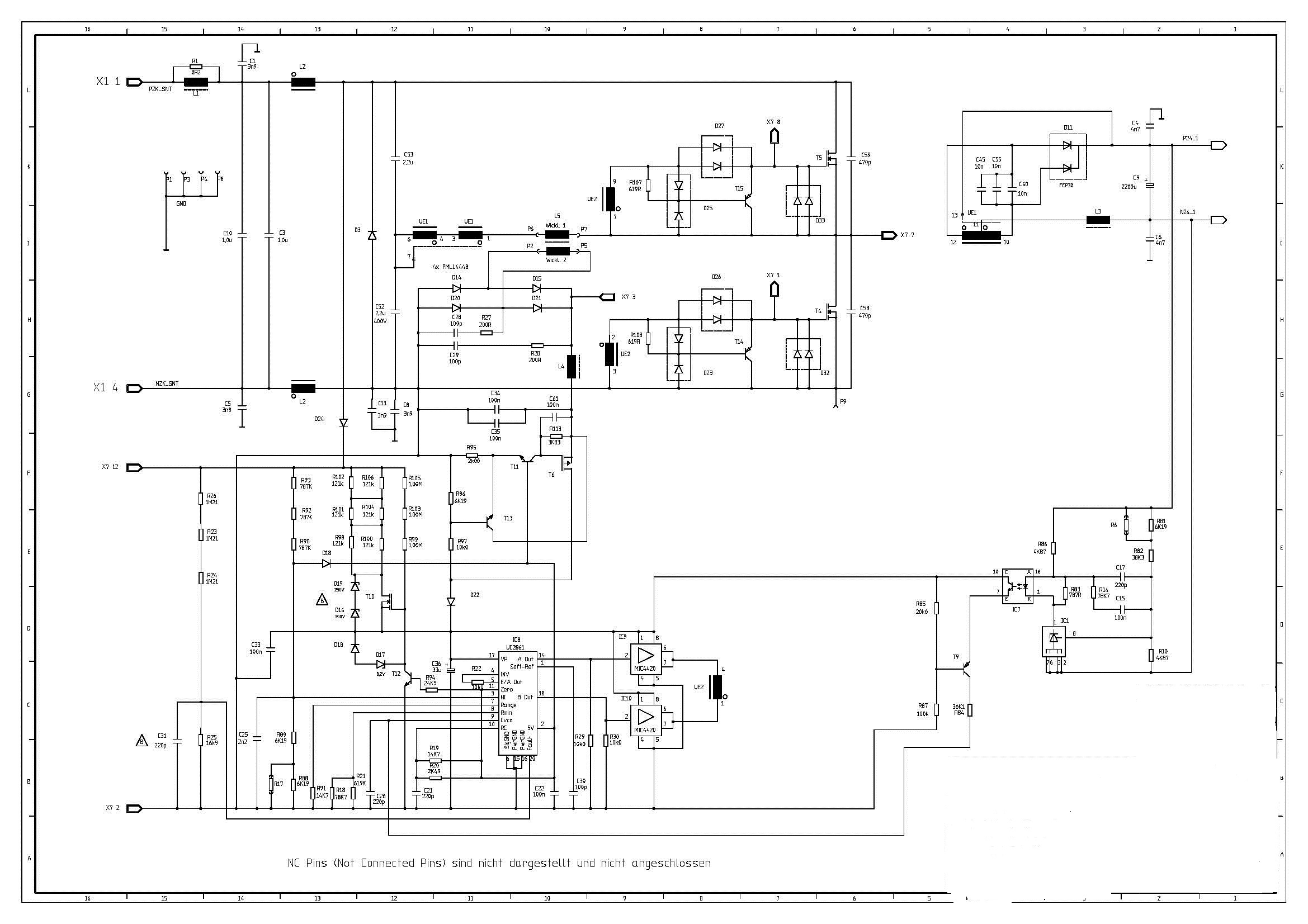

我的客户正在使用 UC2861。 请参阅下面的原理图。 它用于将 DC440V 输入转换为 DC24V 输出。

请注意:

1.X1-1和 X1-4是主电源输入、额定电压为440V。 该440V 输入还通过二极管 D24为 X7-12和 X7-2供电。 x7-12和 x7-2是 驱动器电路的电源。

2. UE2是用于隔离式驱动器的变压器。 1-4是初级侧。 7-9和2-3是次级侧。

3. UE1是将 DC440V 输入转换为 DC24V 输出的主电源变压器。 4-6和3-1为初级侧。 12-10是次级侧。

在实验室测试期间、为了确保系统安全、我们仅使用440VDC 输入为 X7-12和 X7-2供电。 我们没有为 X1-1和 X1-4供电。 这样、只有驱动电路 UC2861上电、主电源电路上电。 因此、我们可以测试 UC2861性能、而无需真正驱动电源电路。

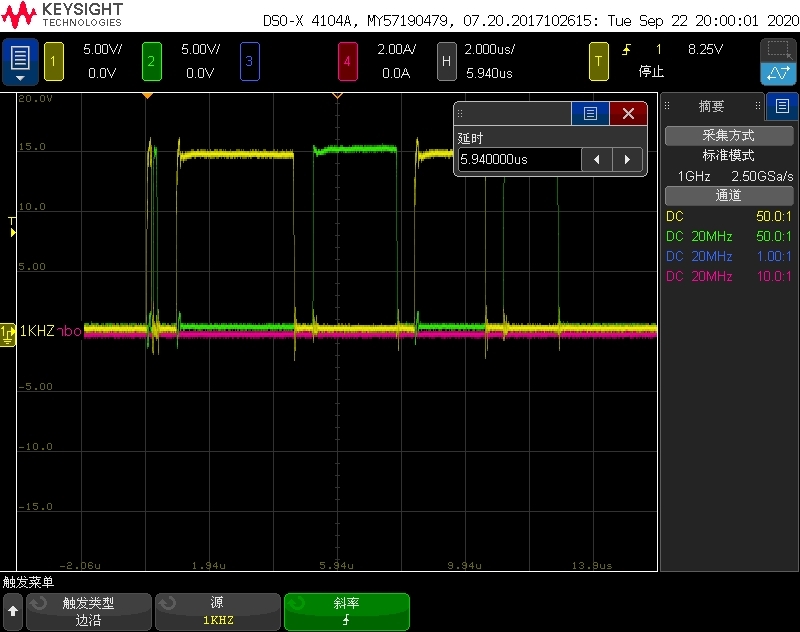

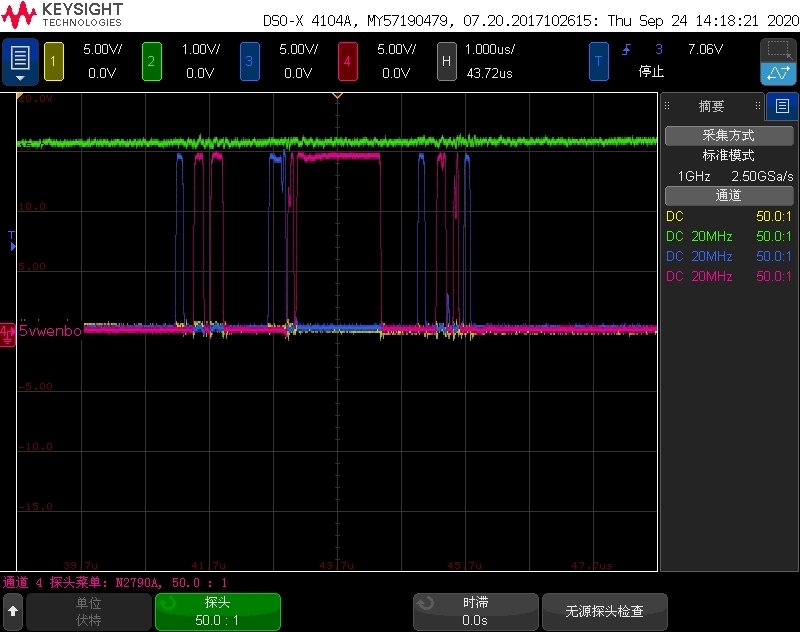

进行过压测试时、我们将 X7-12和 X7-2之间的电压从440V 增加到650V。 理论上、UC2861将输出几个脉冲、然后关闭脉冲输出。 我们的测试波形如下所示:

CH1=UC28OD 的 AOUT 引脚。 CH2=UC28Os BOUT 引脚。 如您所见、Aout 和 Bout 分别输出3个脉冲、然后停止。 但是、Aout 和 Bout 之间的第一个脉冲具有非常短的死区时间、这对于驱动 MOSFET 而言是不安全的。 但稍后、第二个脉冲和第三个脉冲的死区时间变为正常状态。

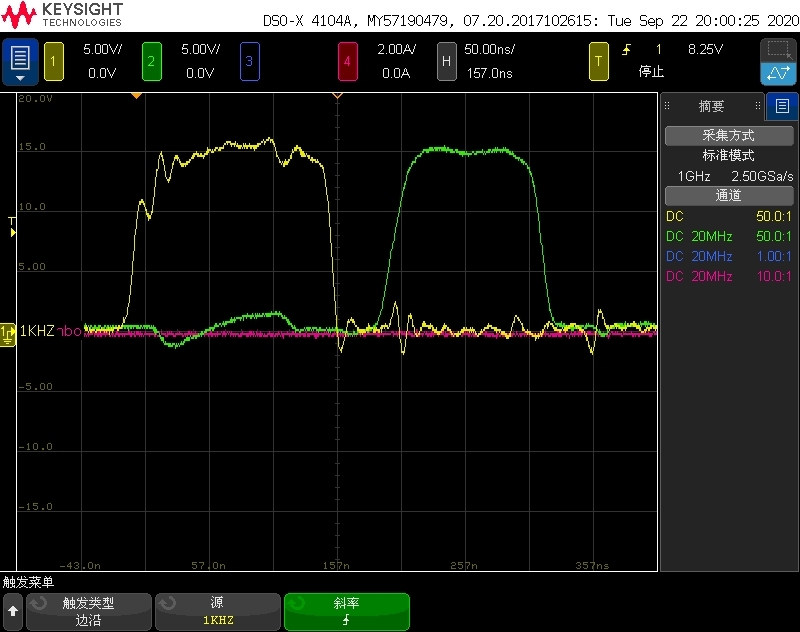

当我们在下图的第一个脉冲中进行求和时、我们可以发现死区时间仅为50ns、这太短了。

那么、您能否帮助告知为什么在过压测试条件下第1个脉冲具有如此短的死区时间? 我们如何调整电路使其正常? 谢谢。

此致、

韦恩