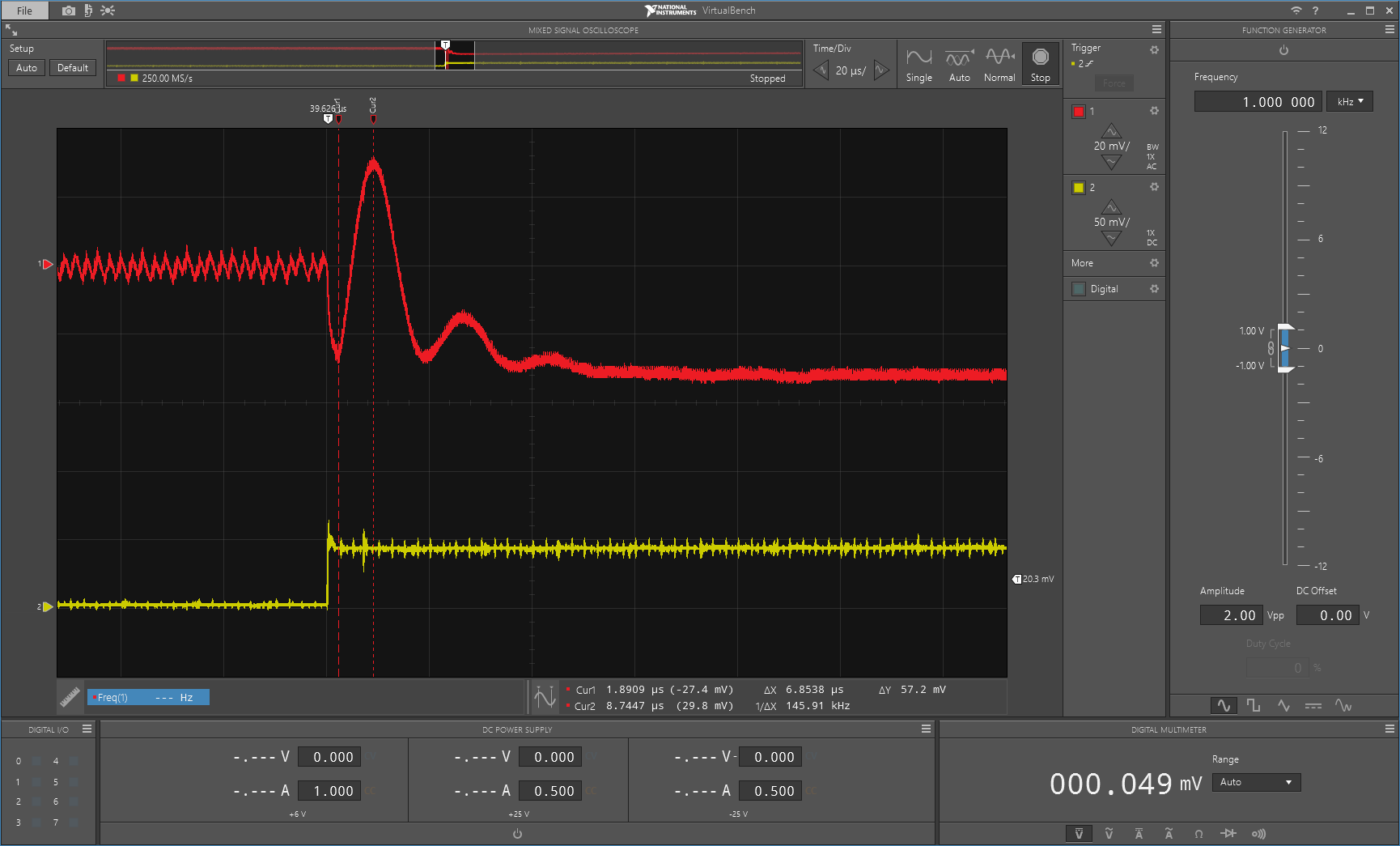

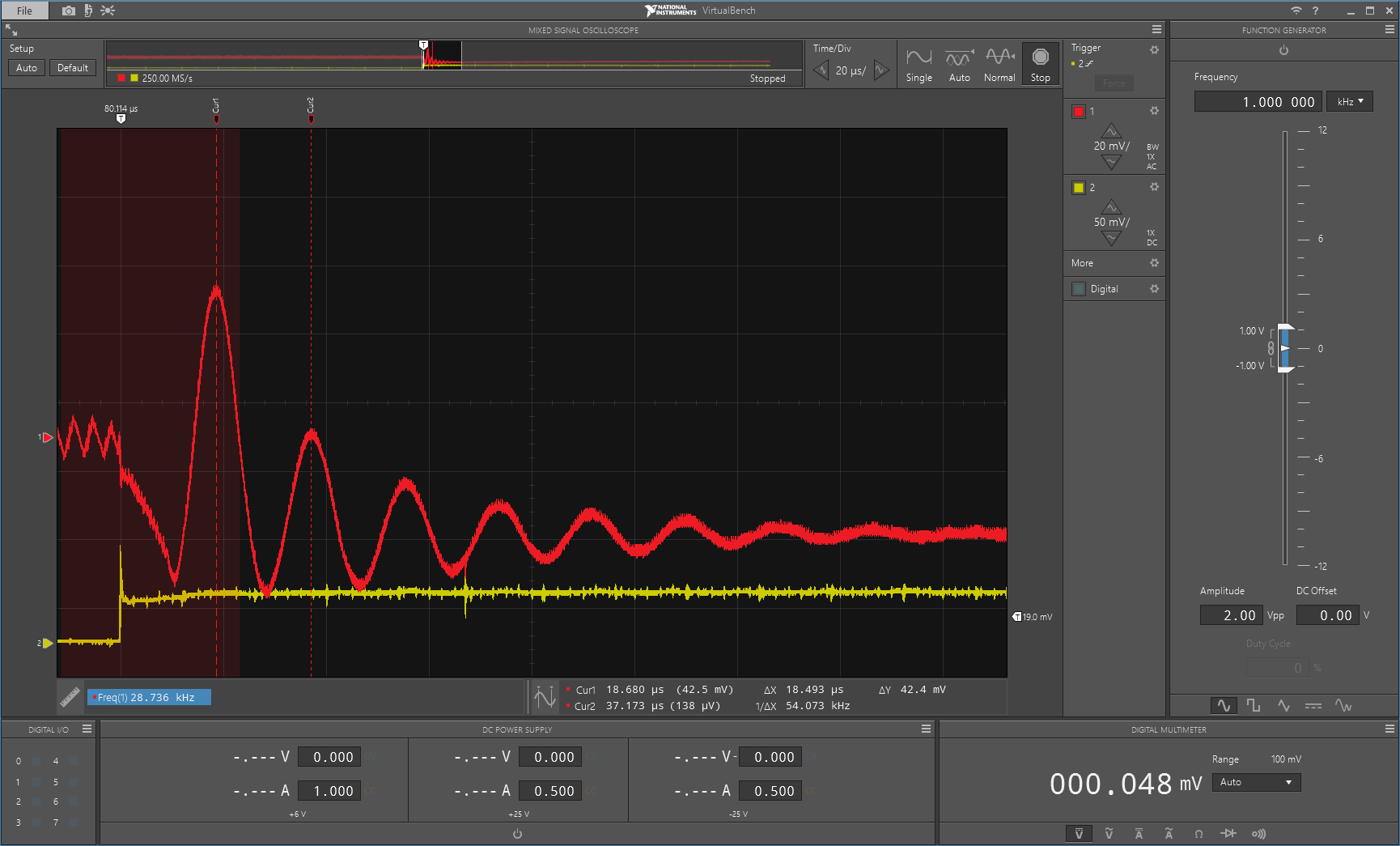

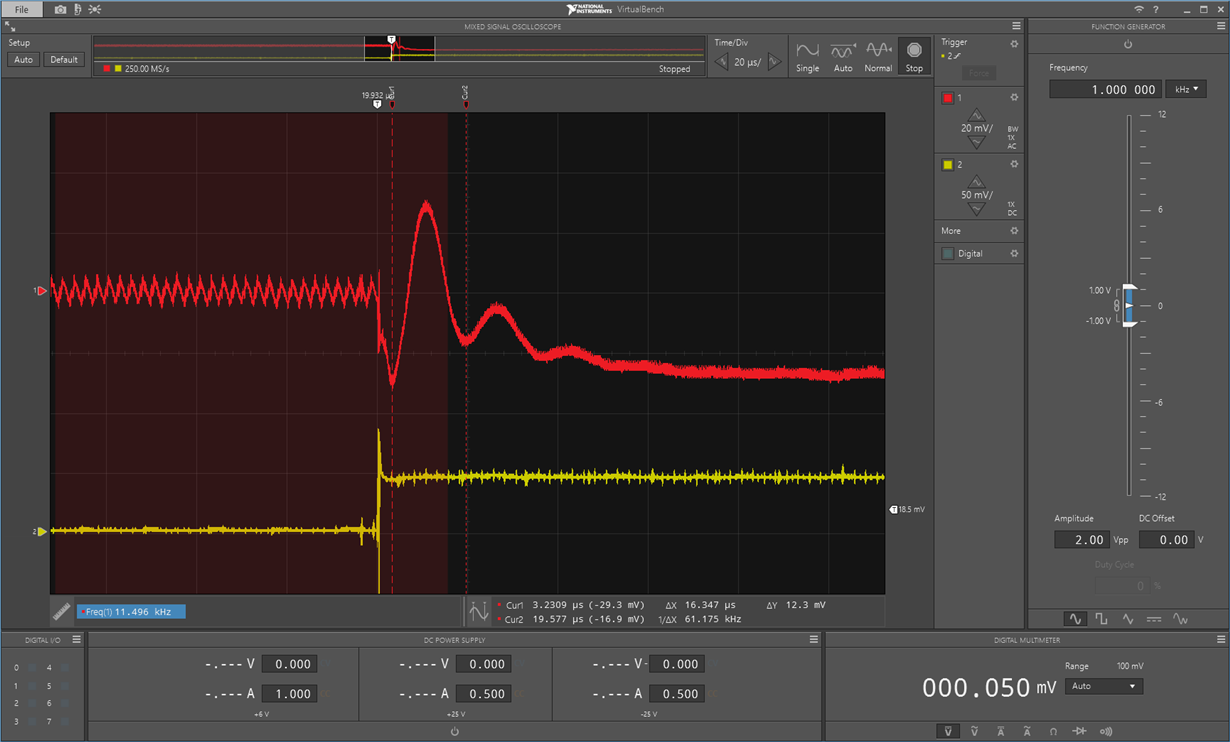

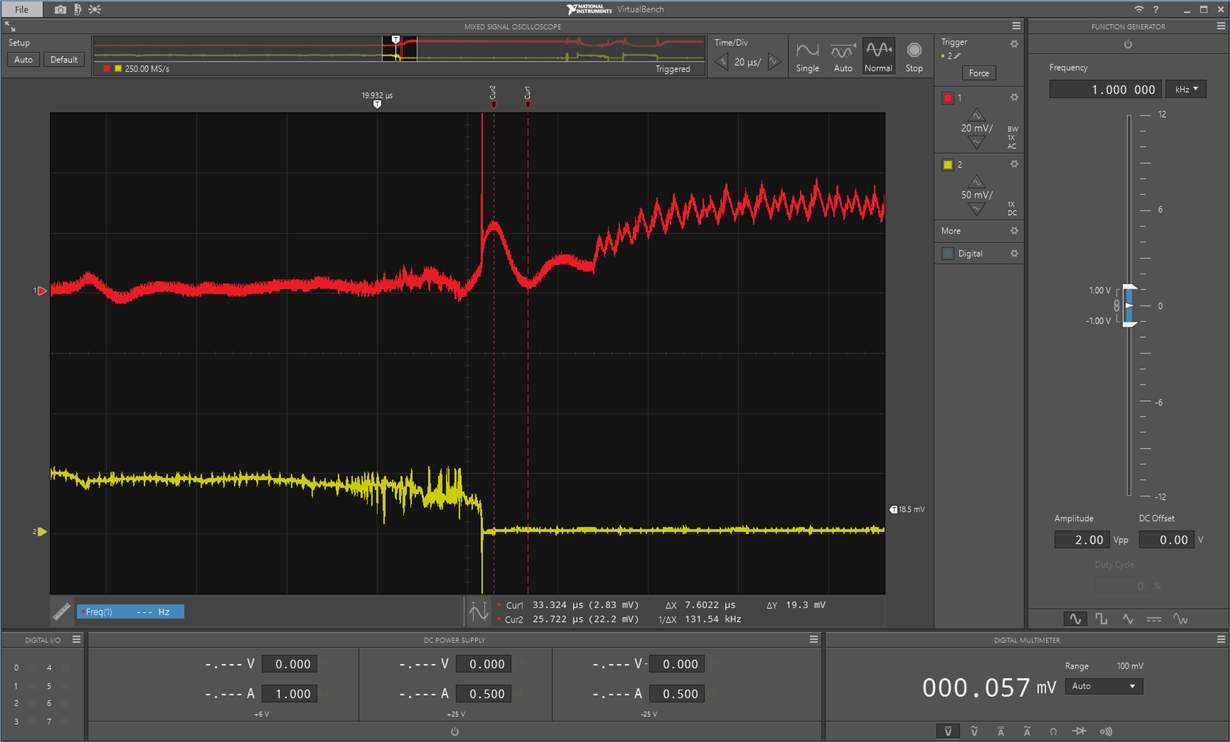

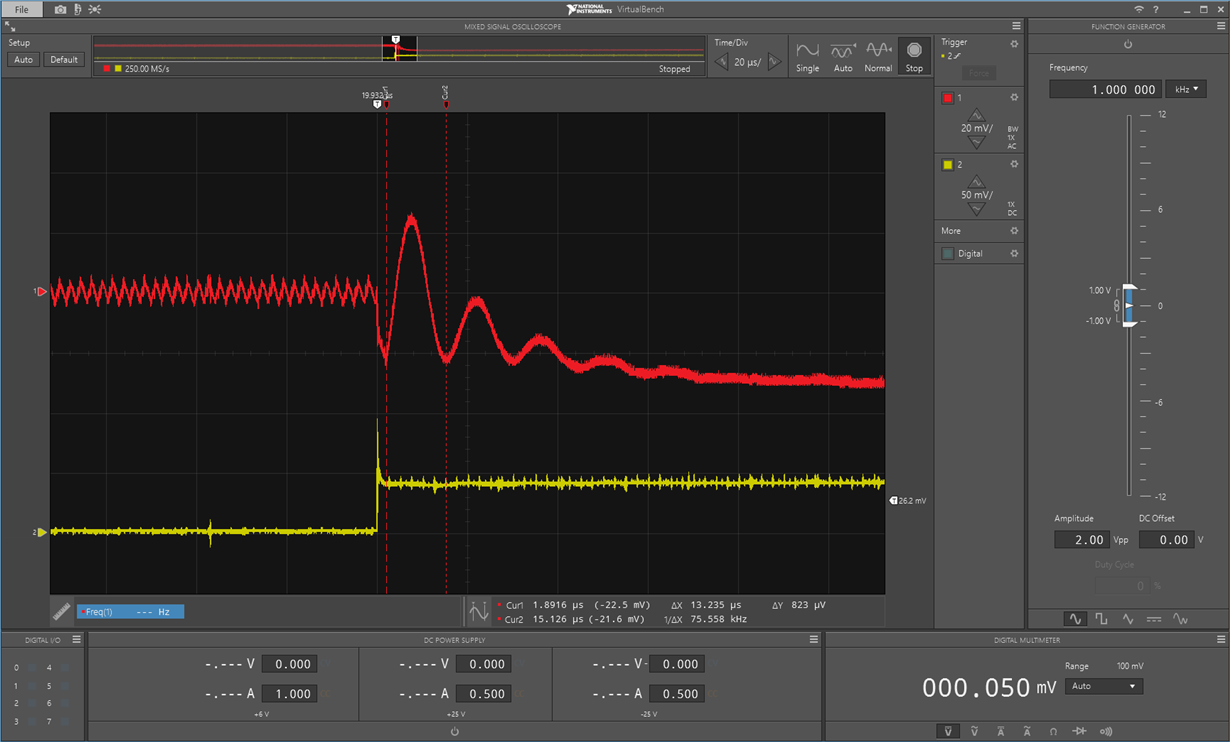

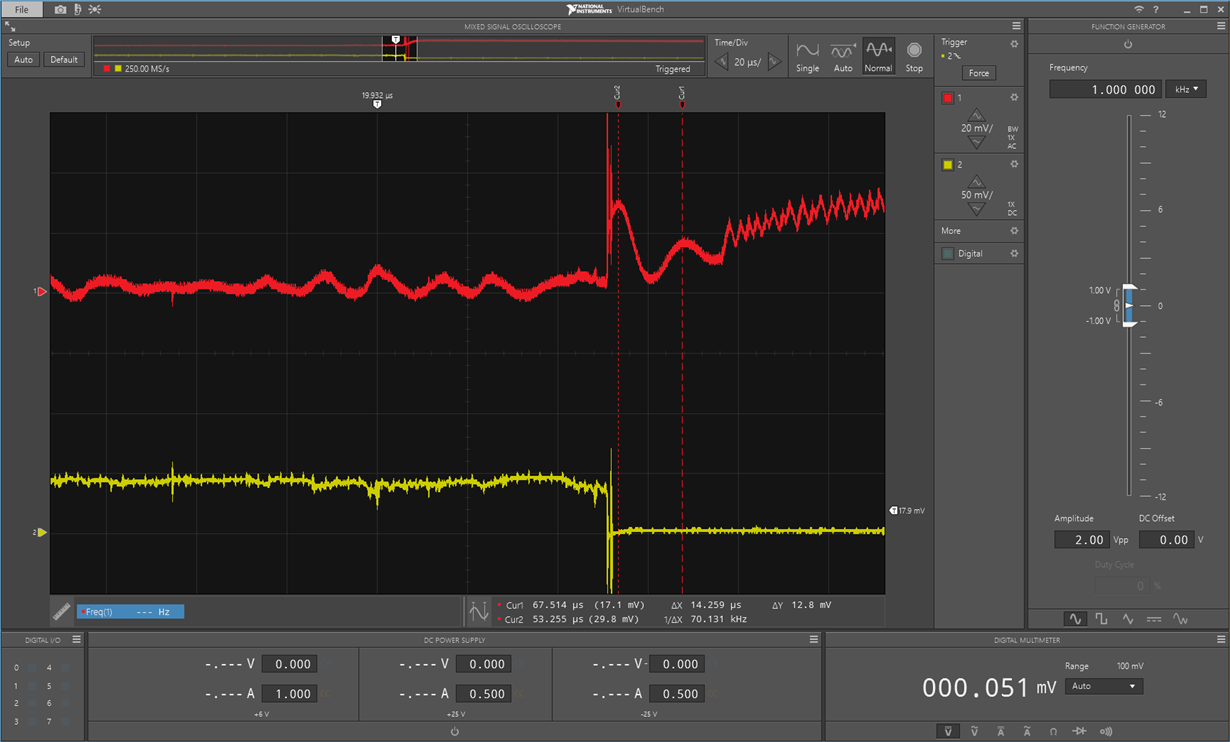

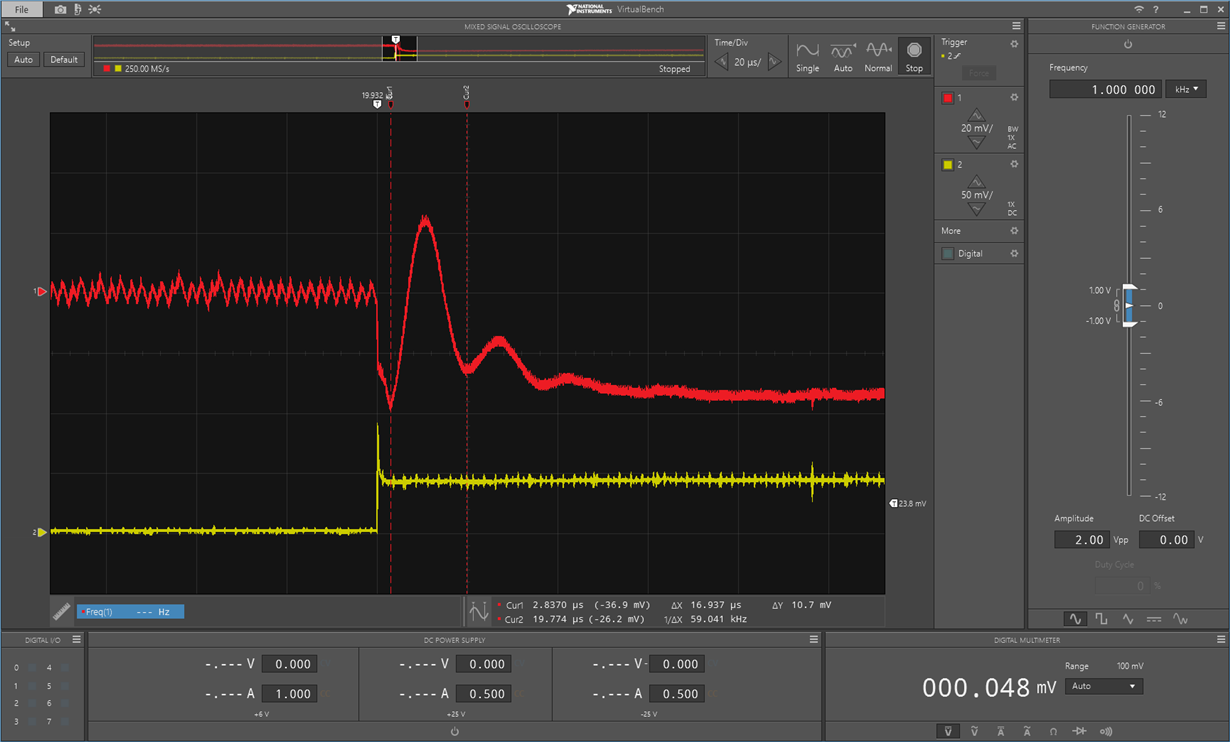

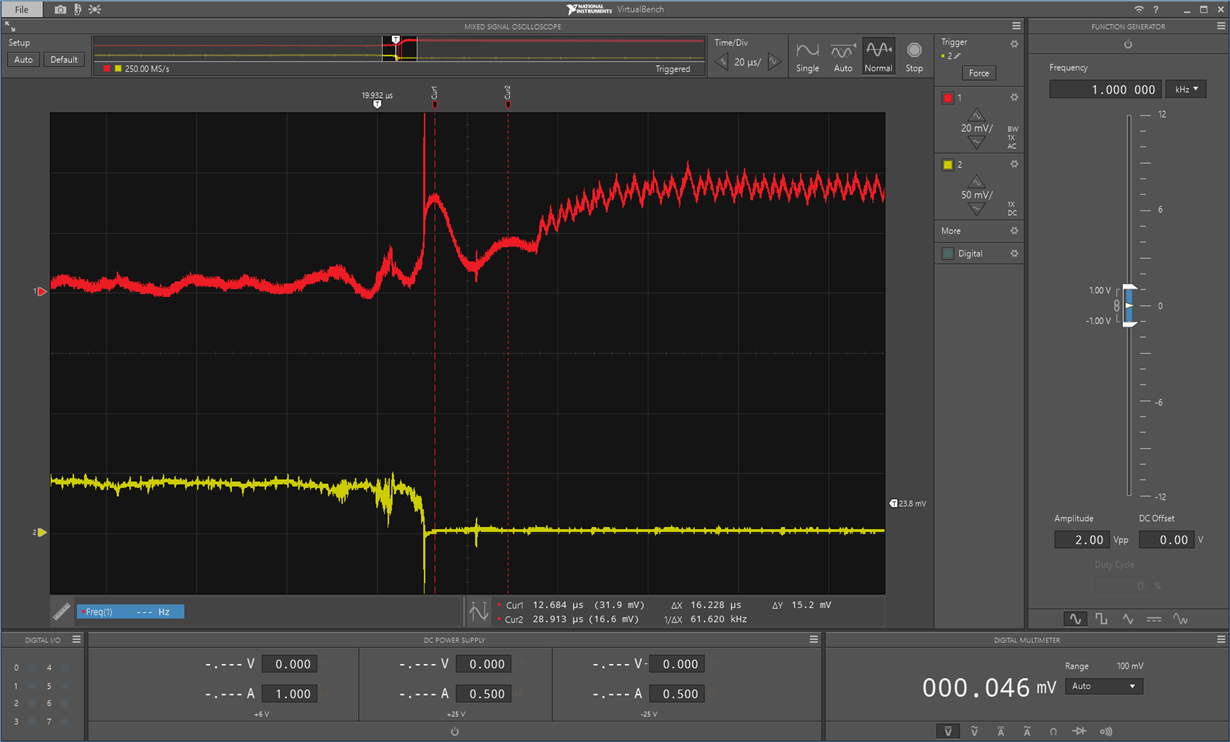

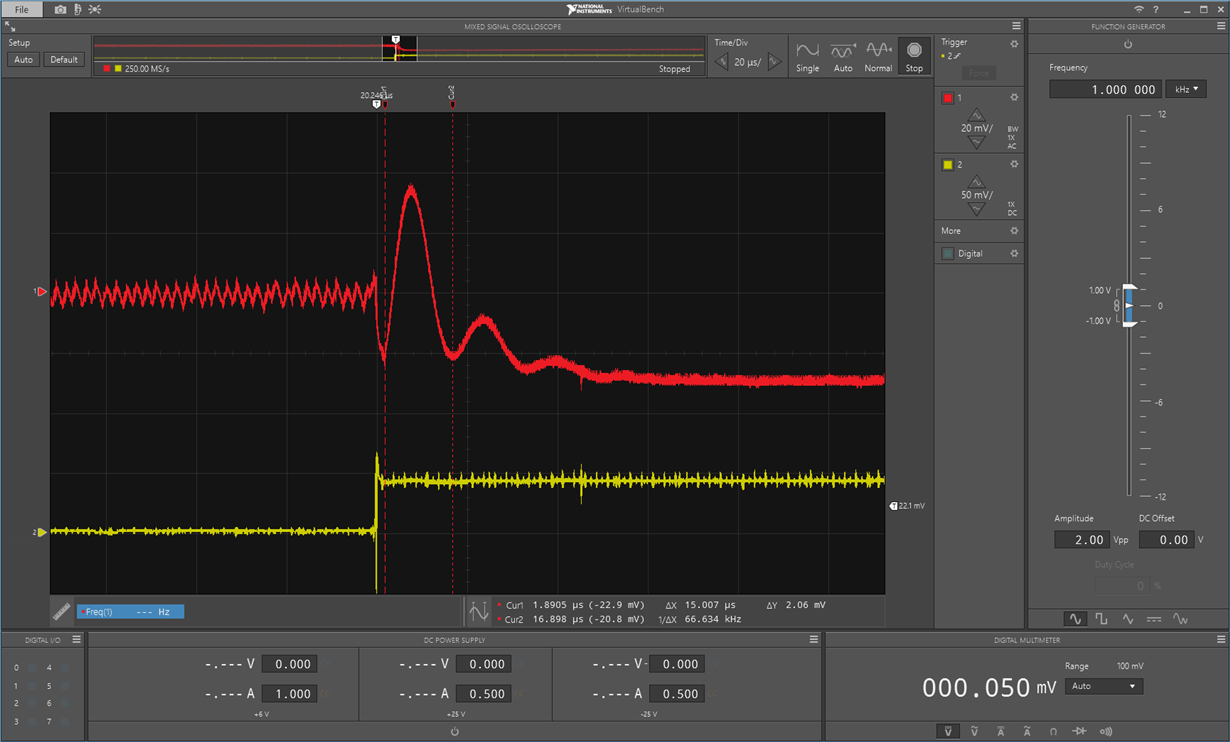

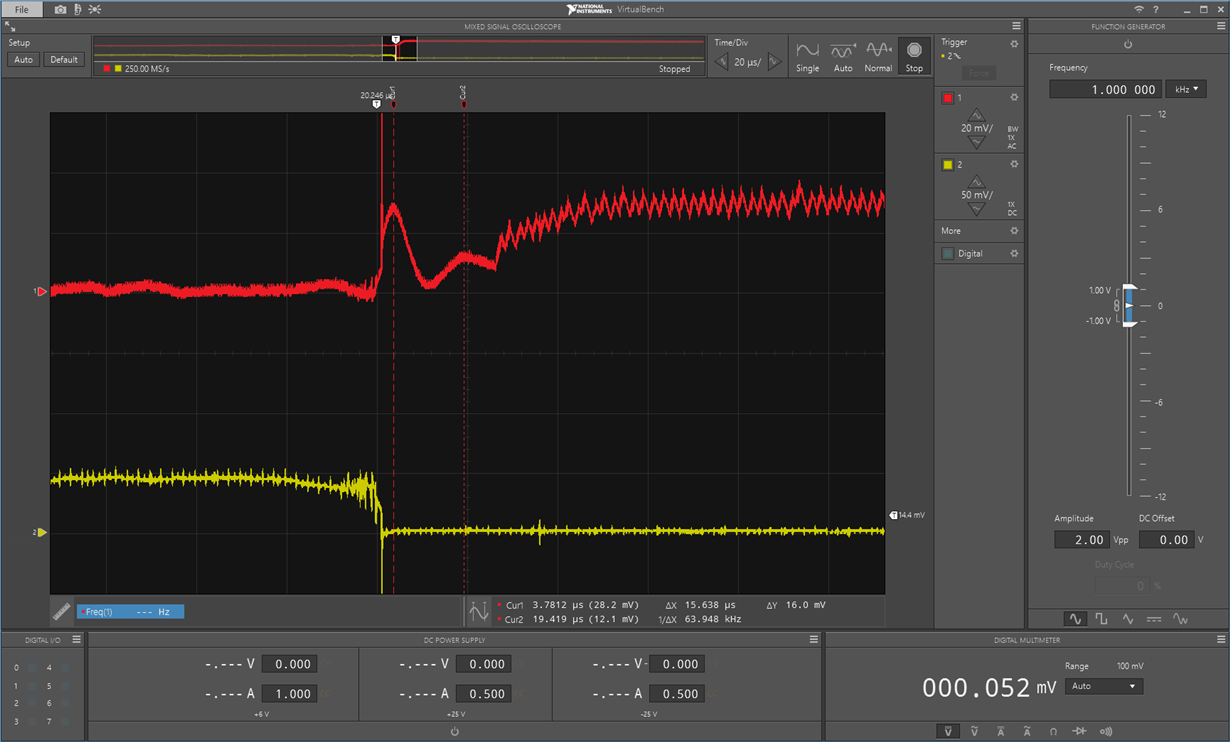

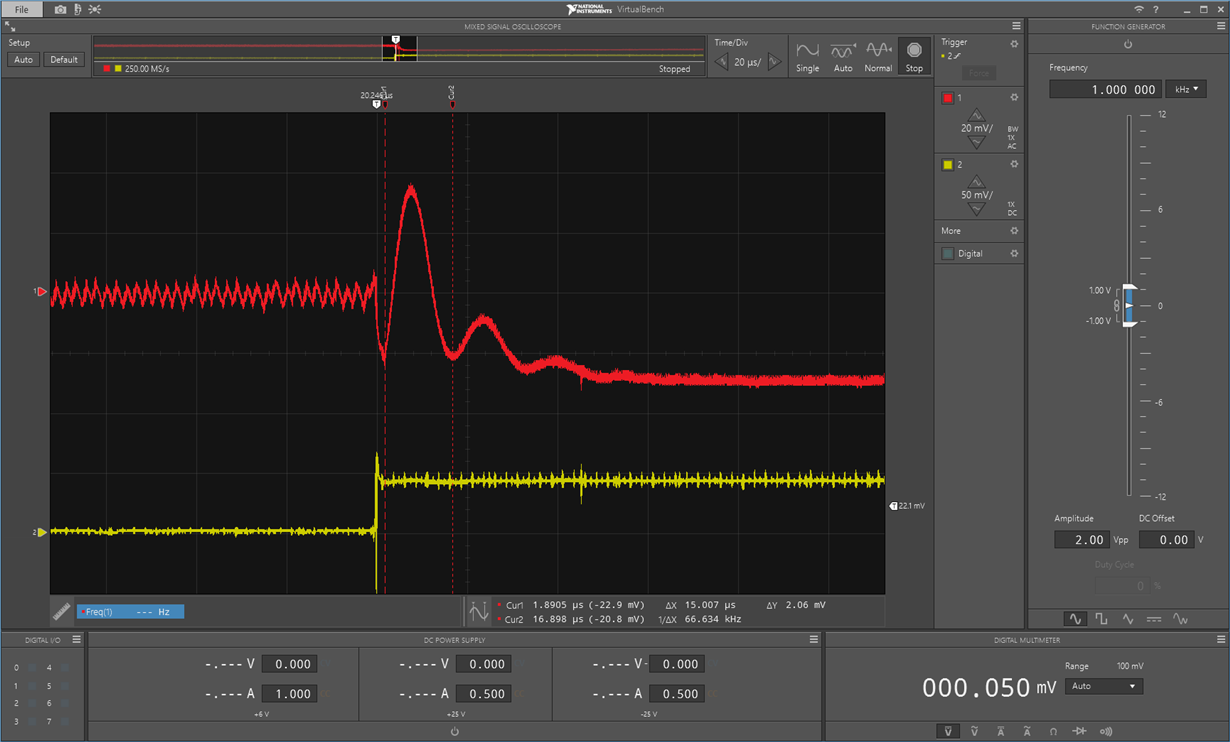

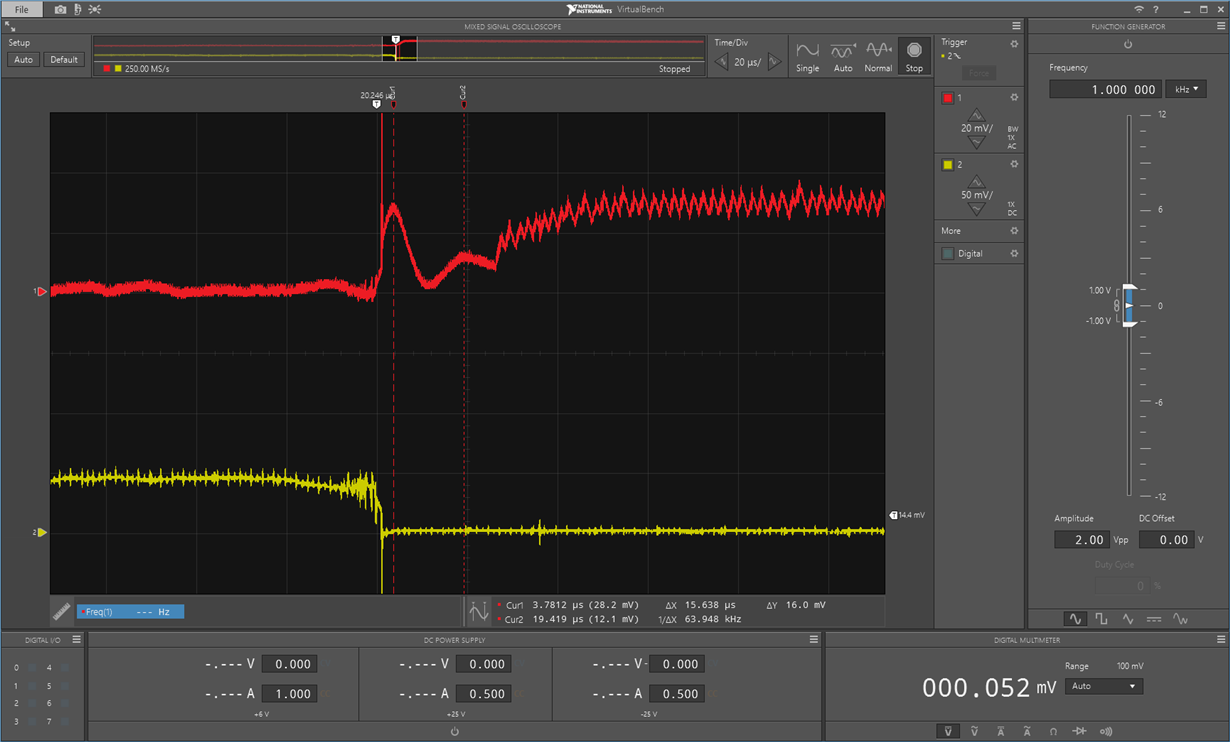

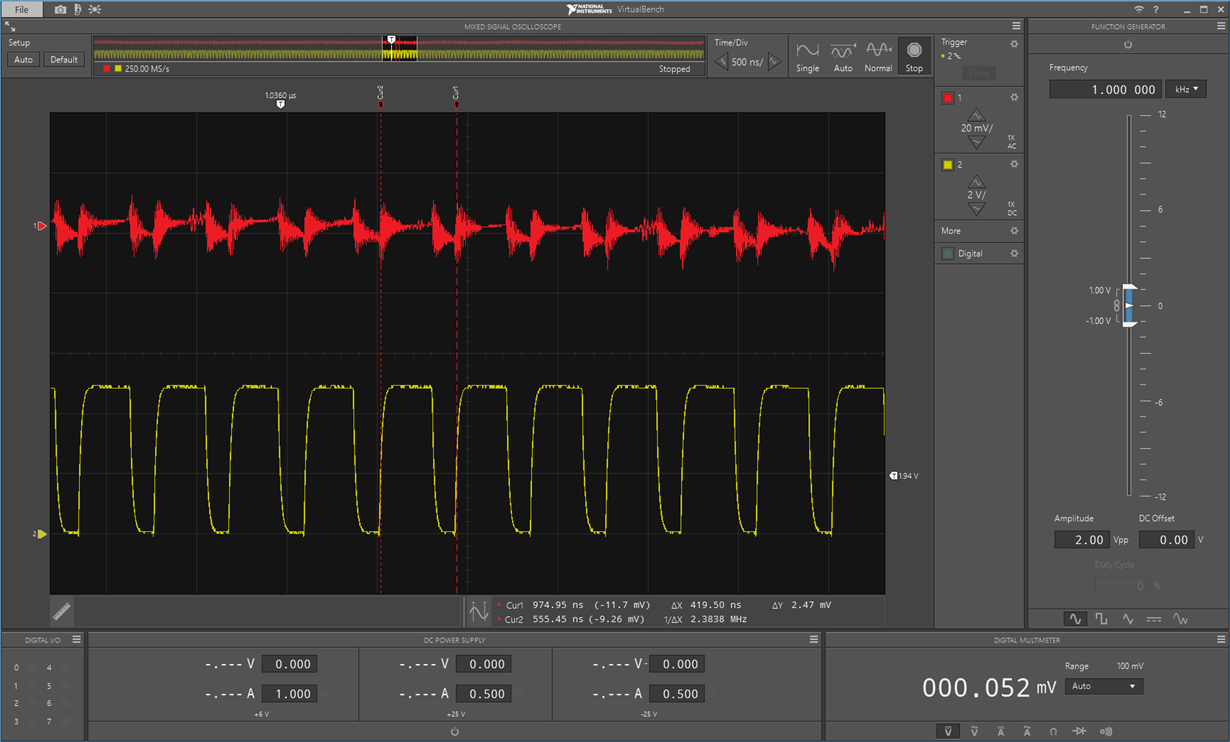

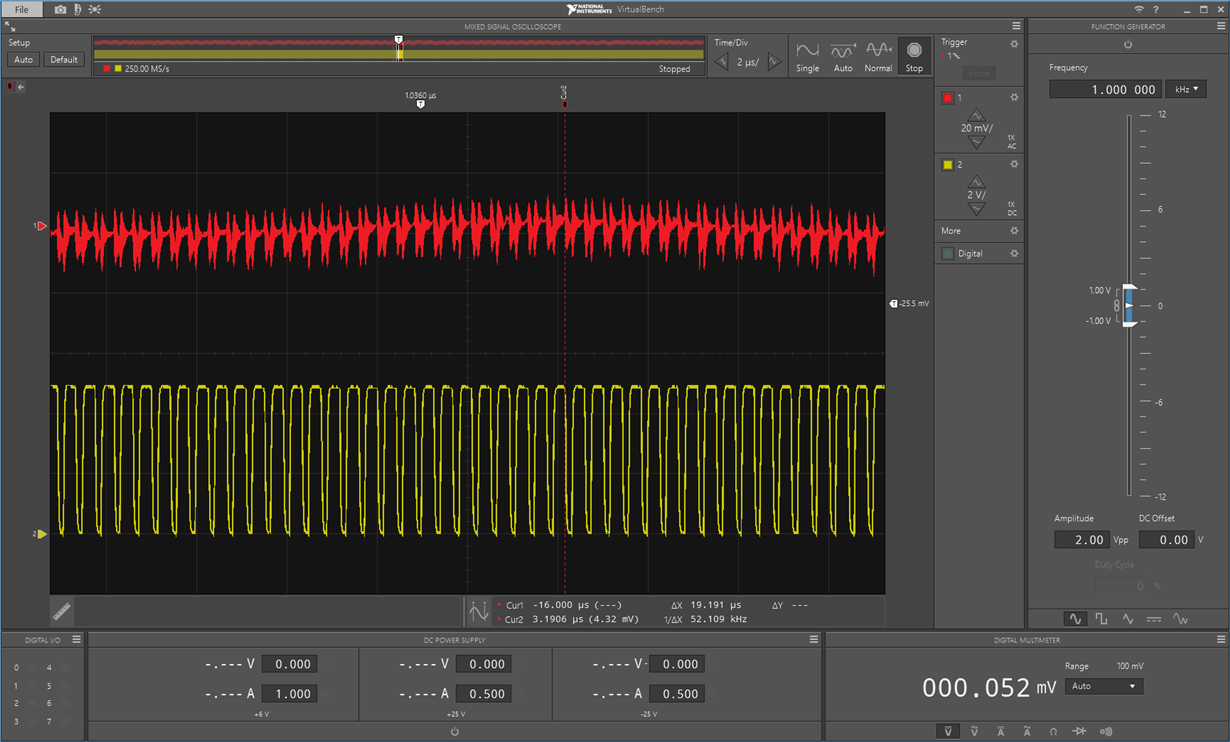

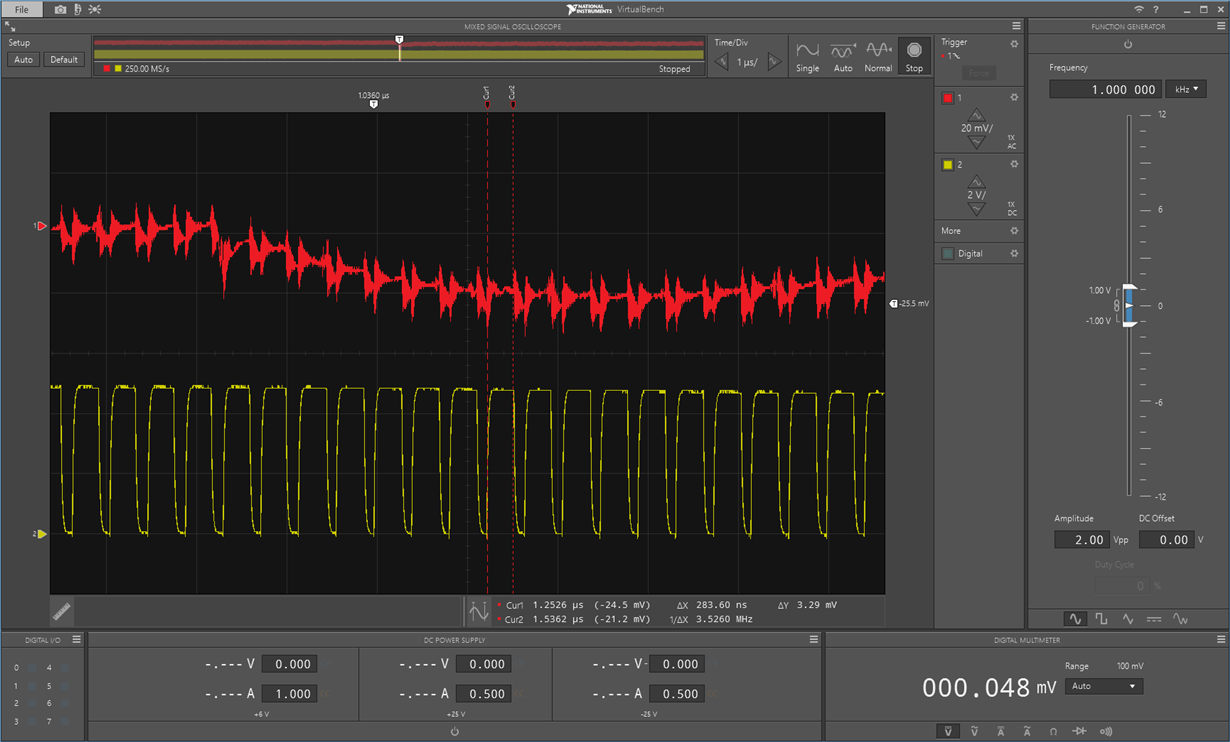

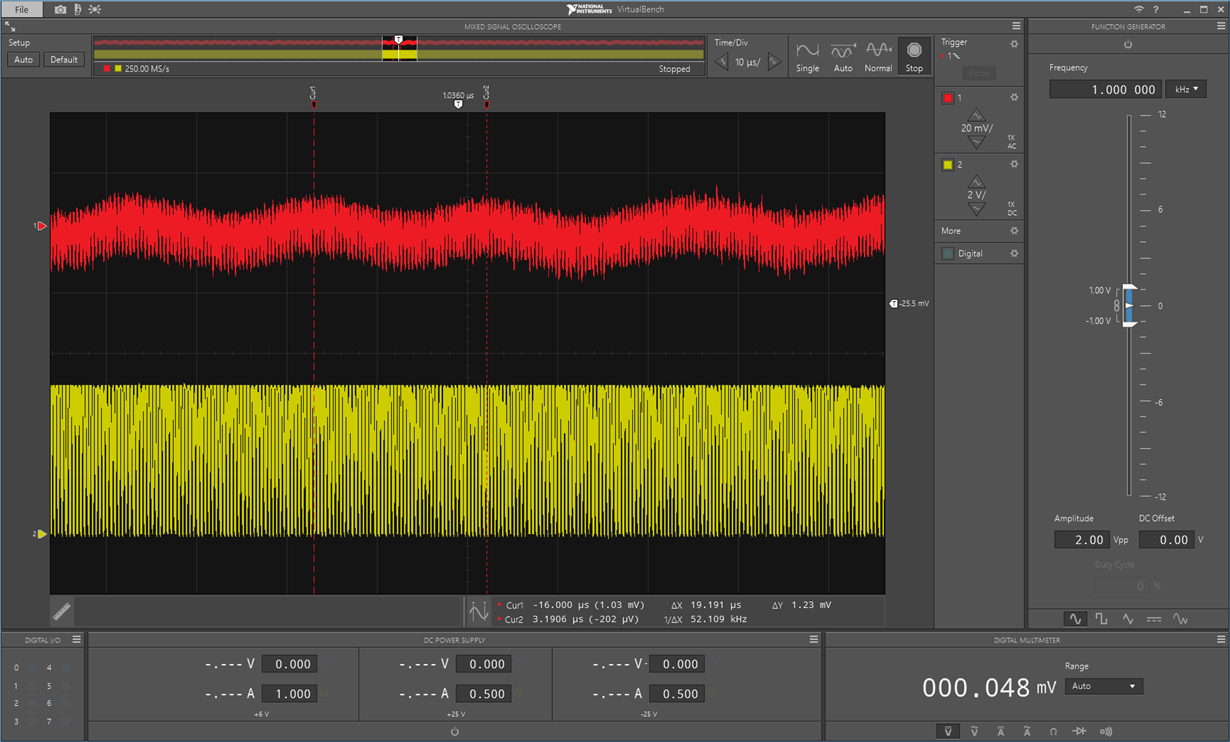

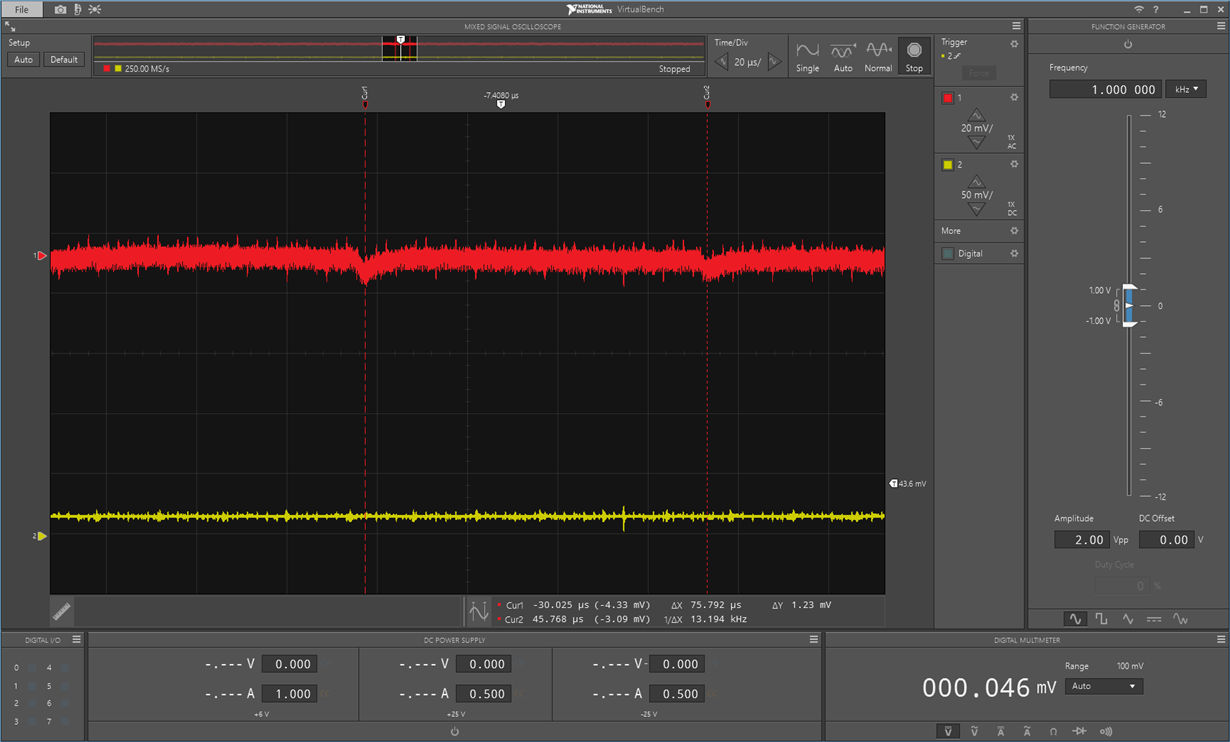

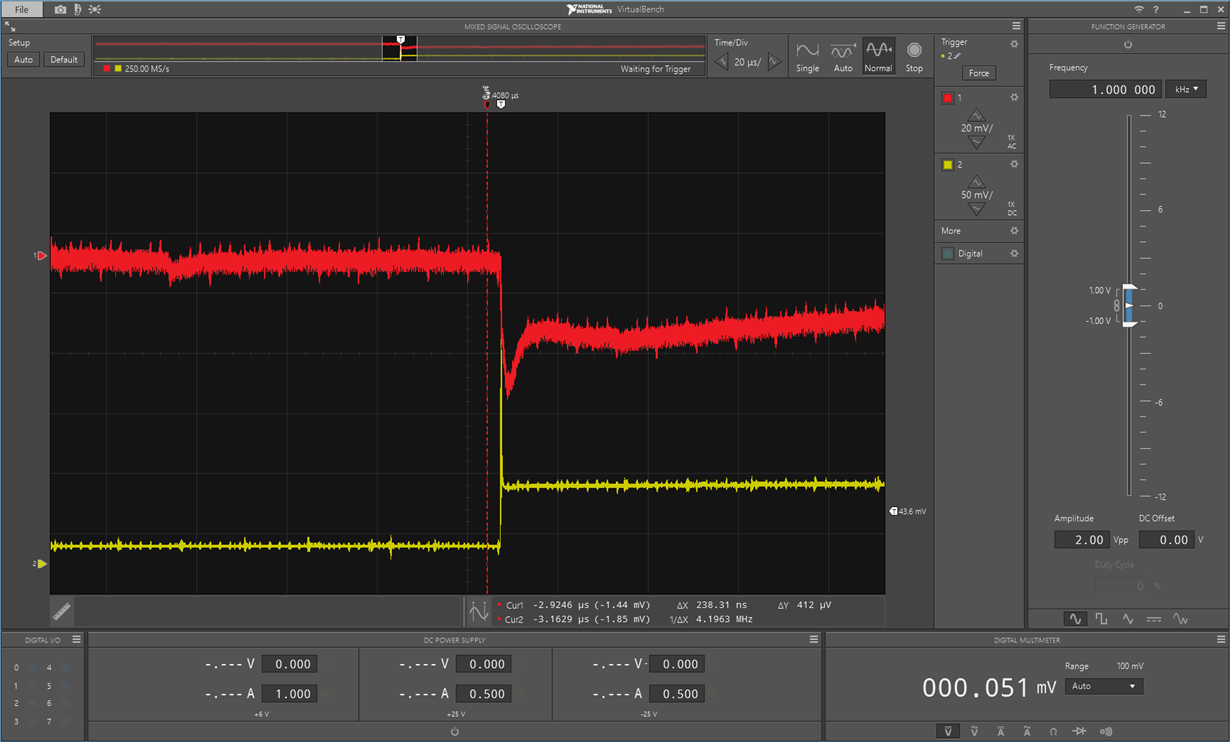

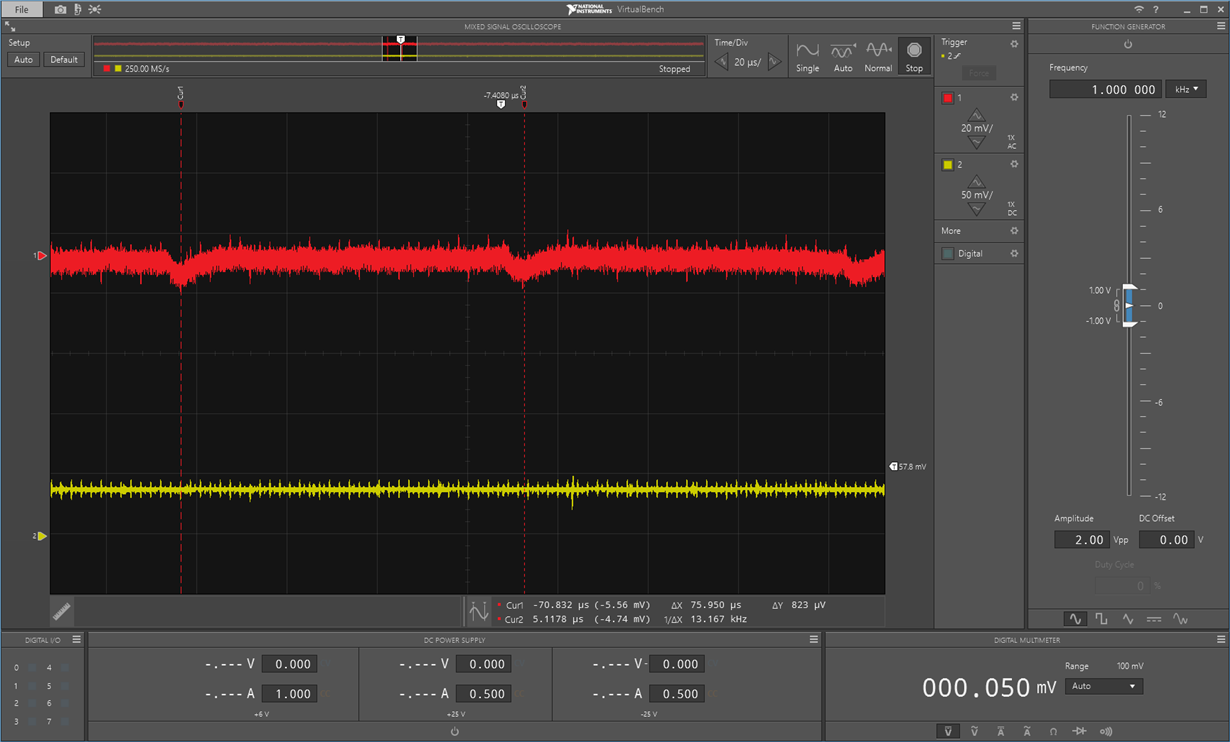

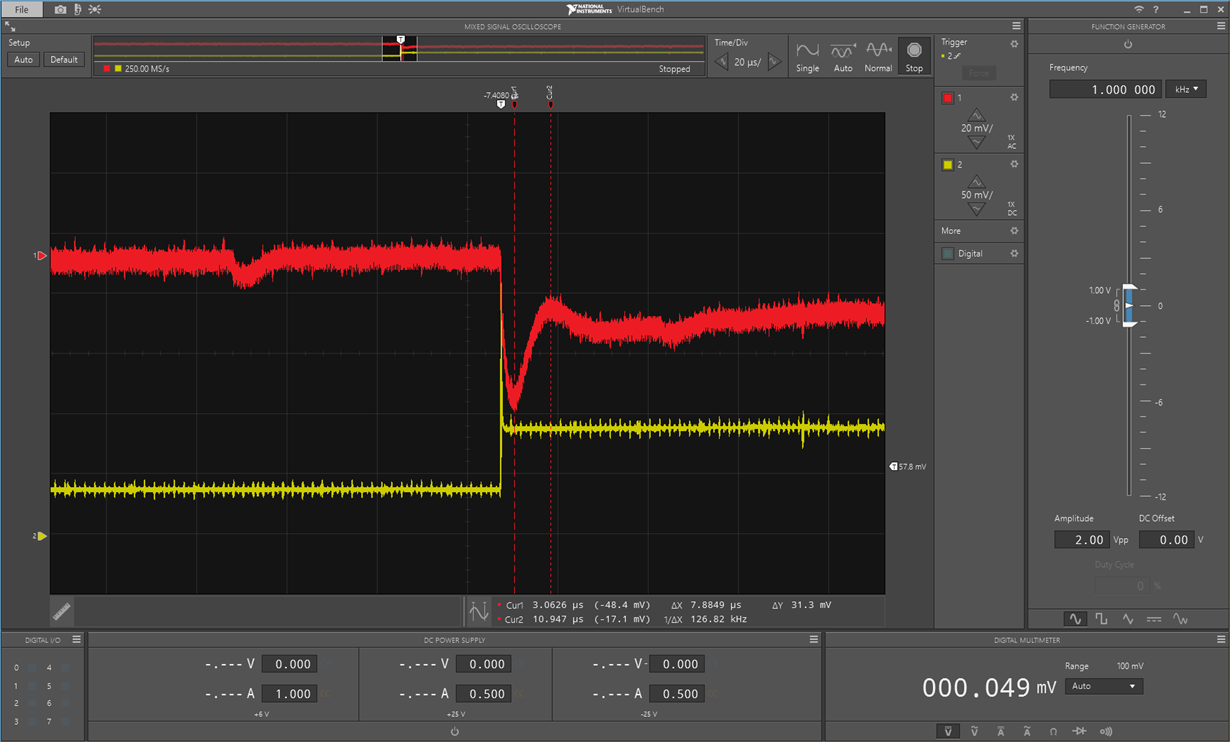

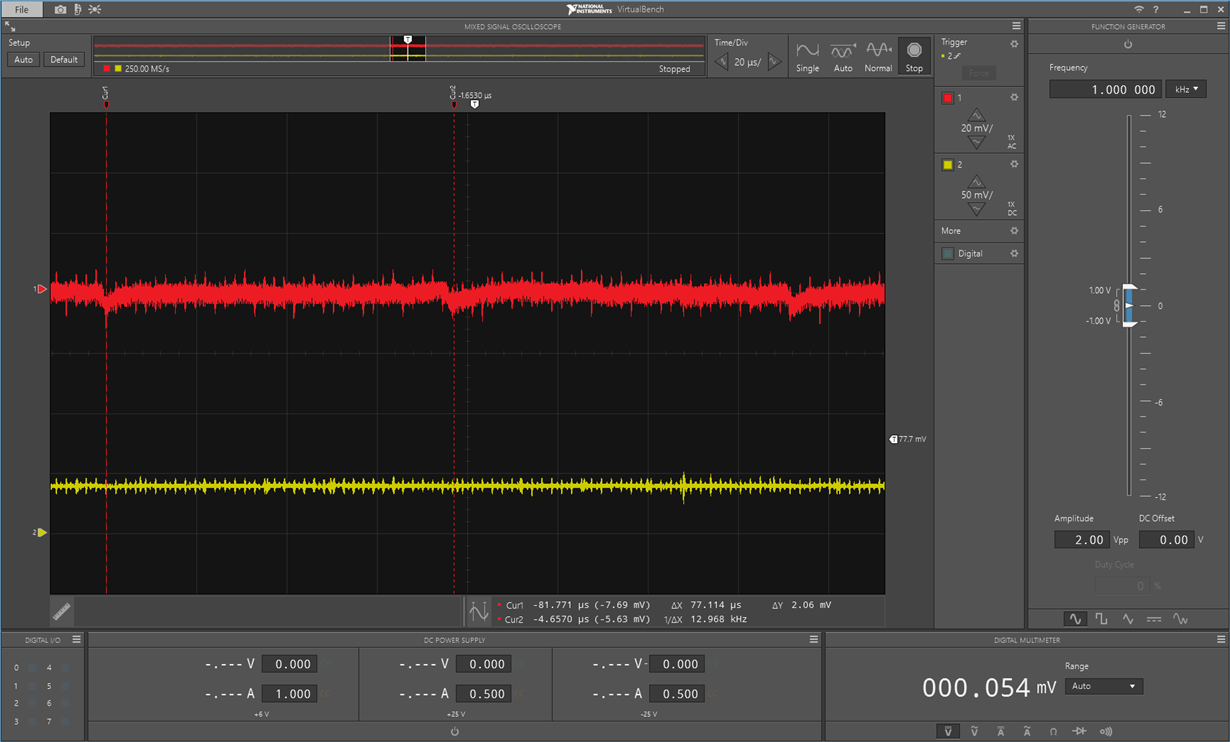

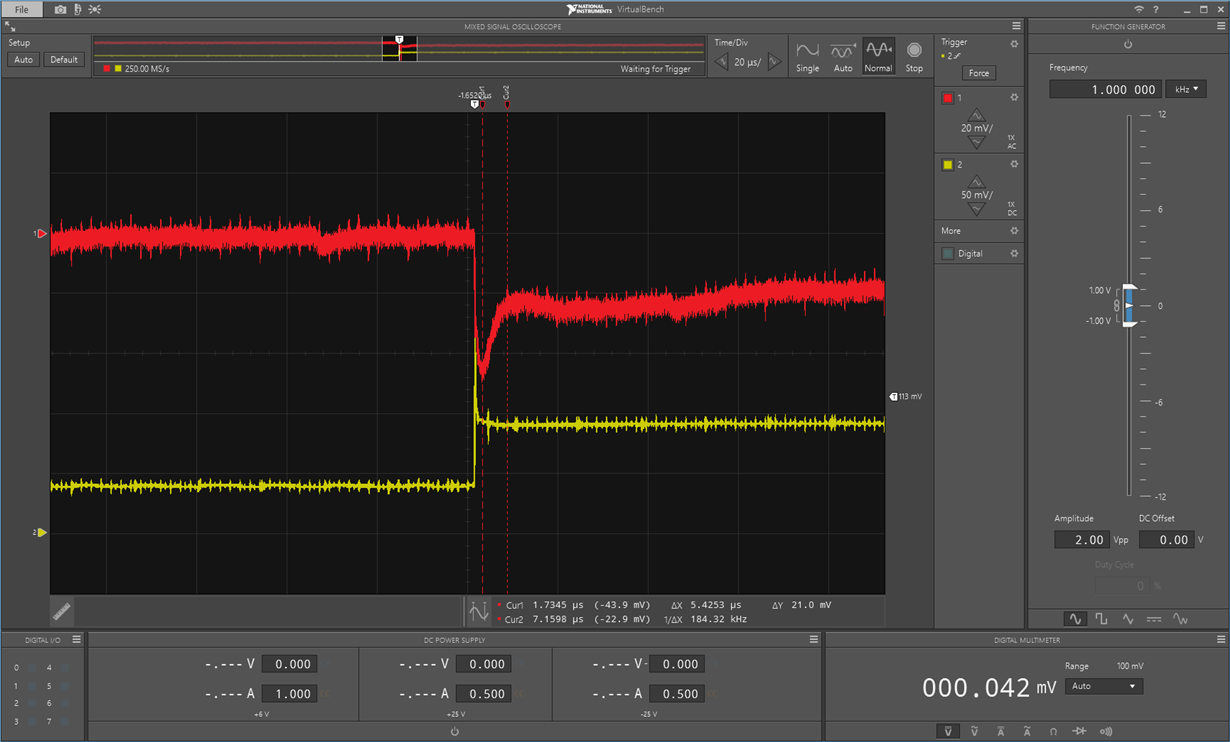

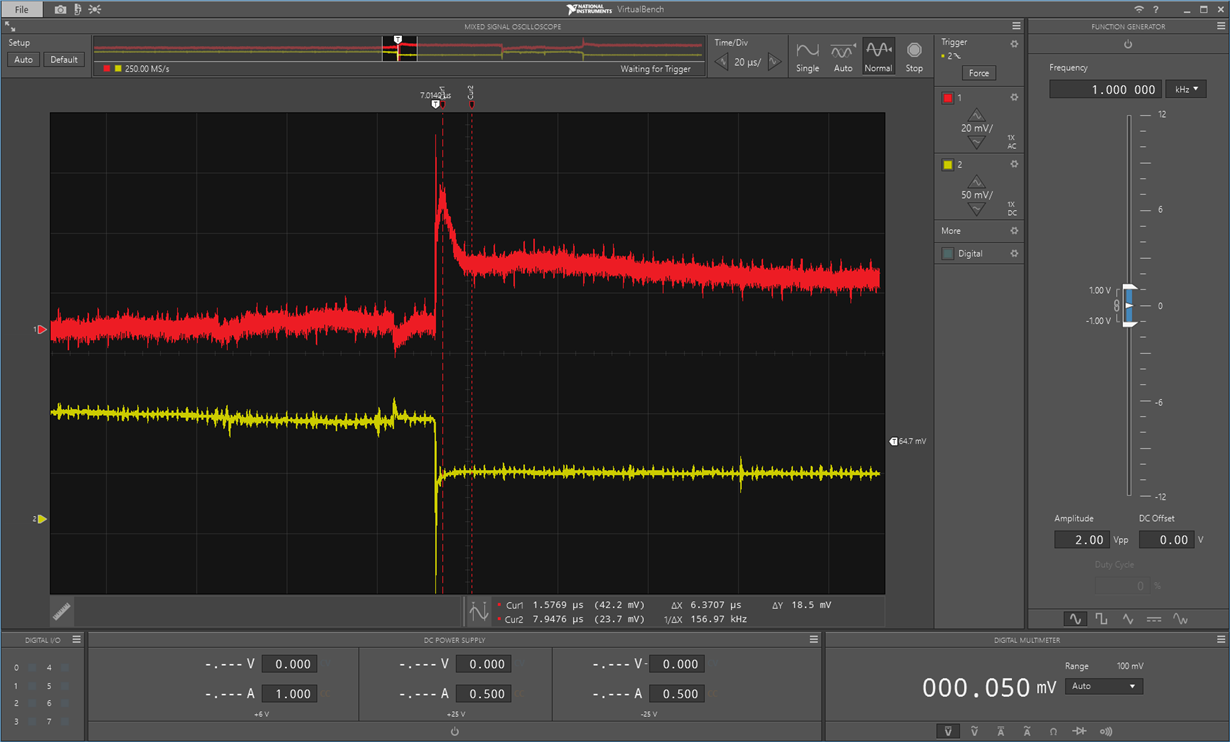

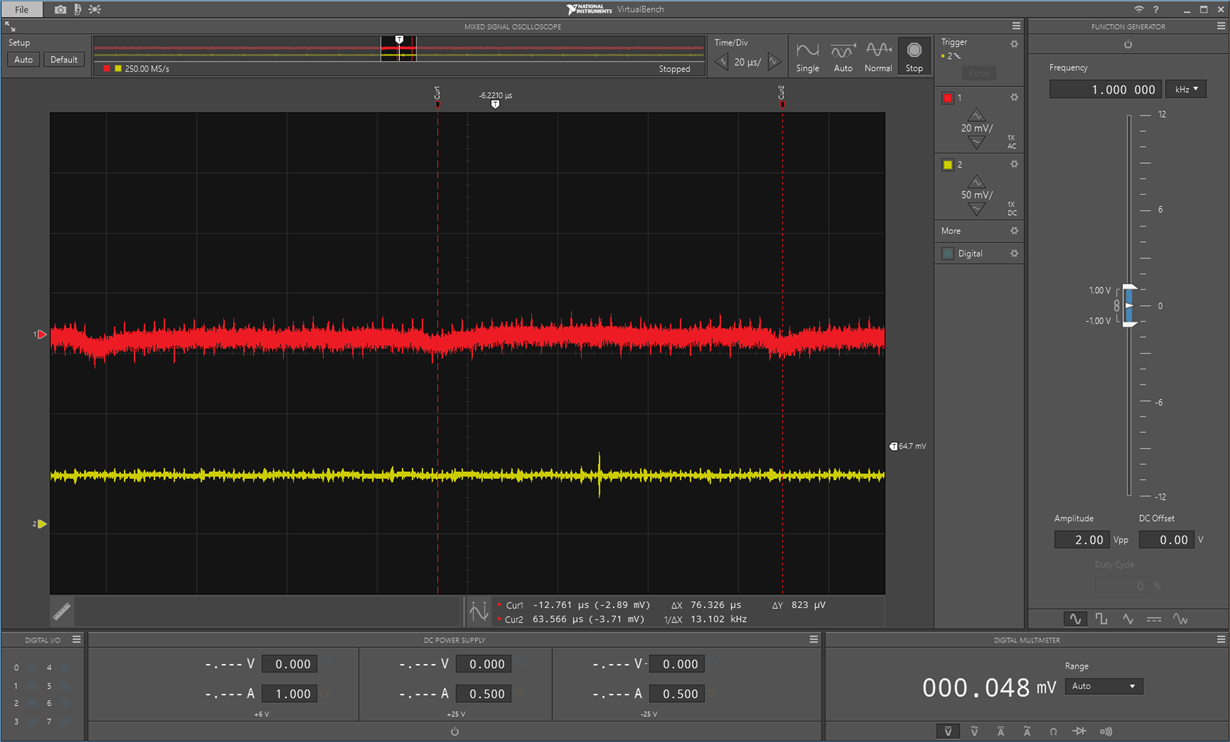

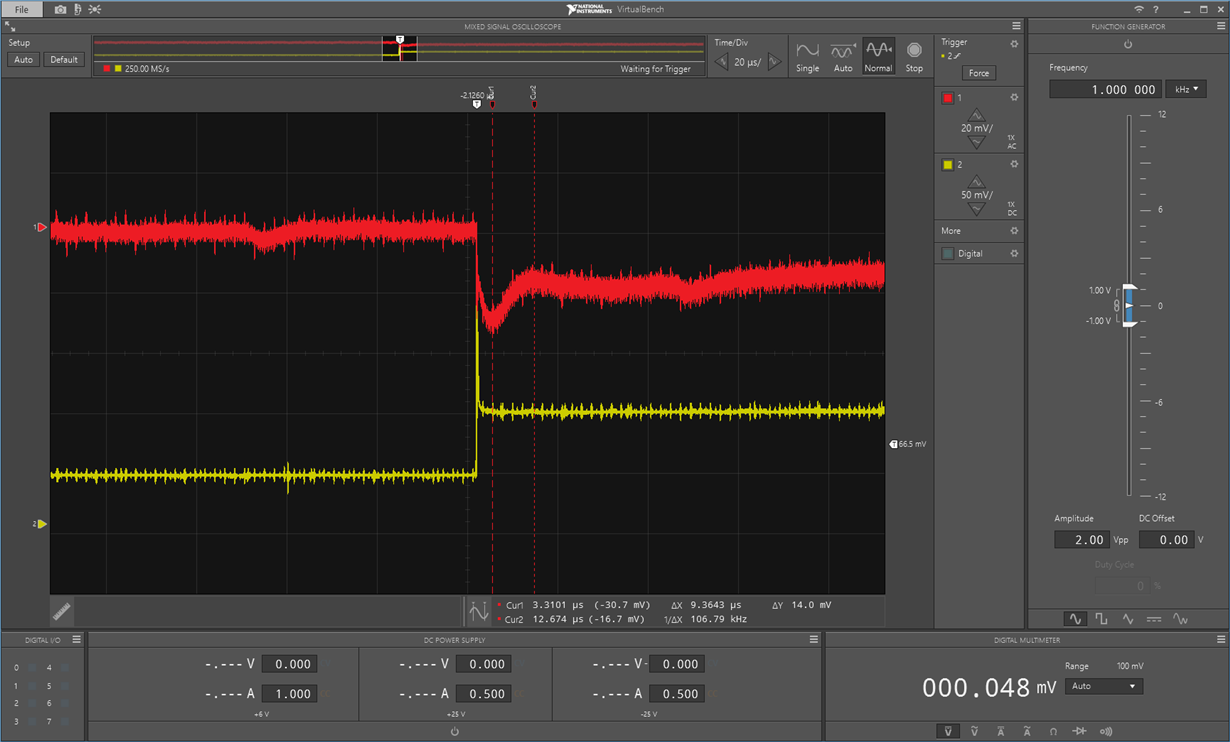

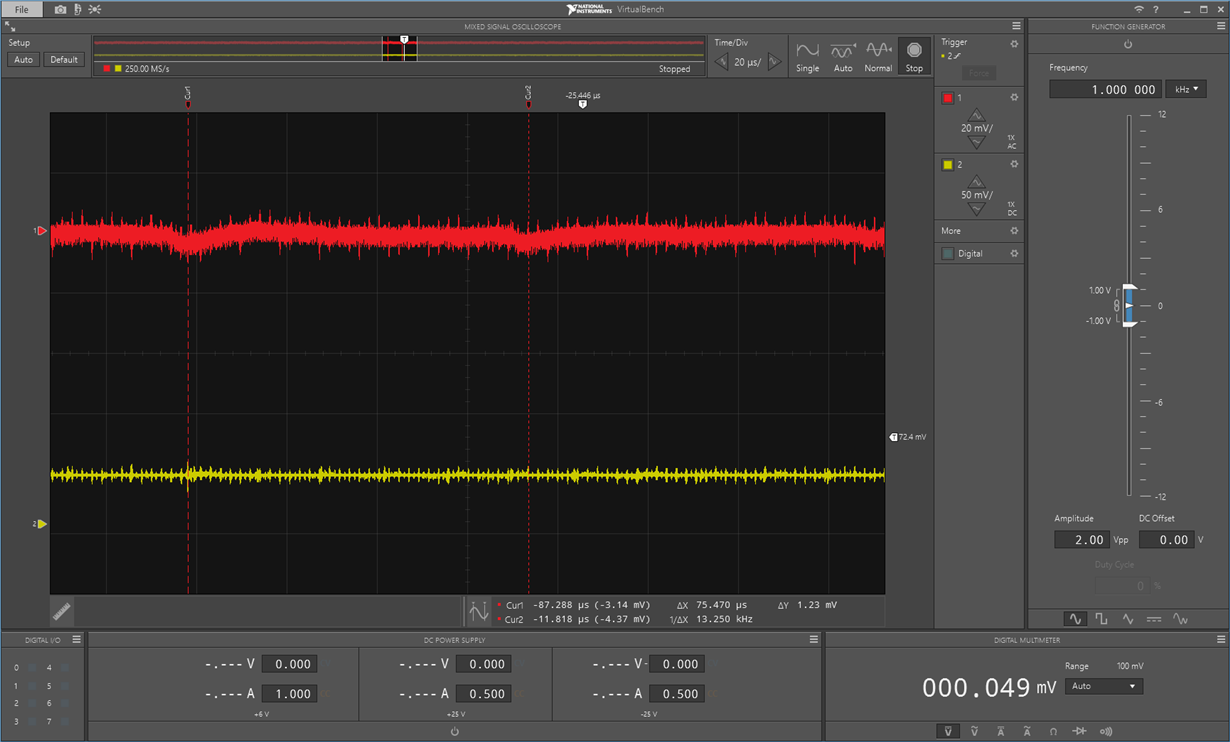

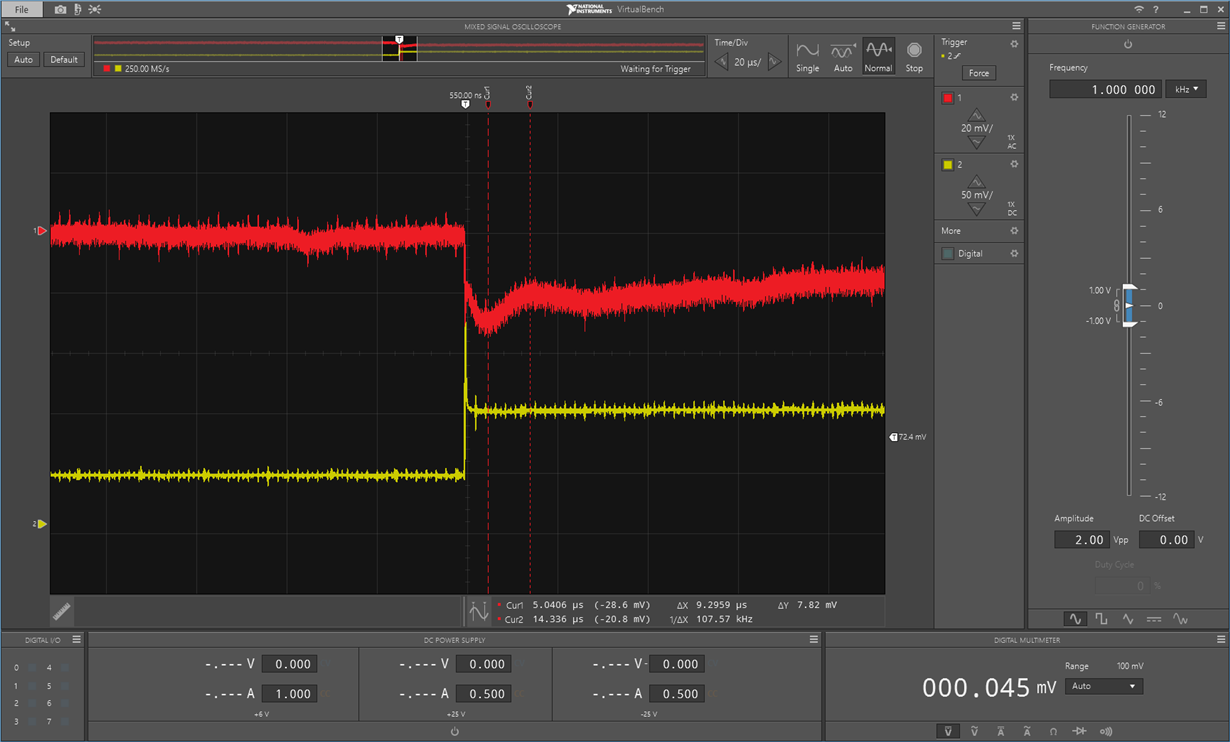

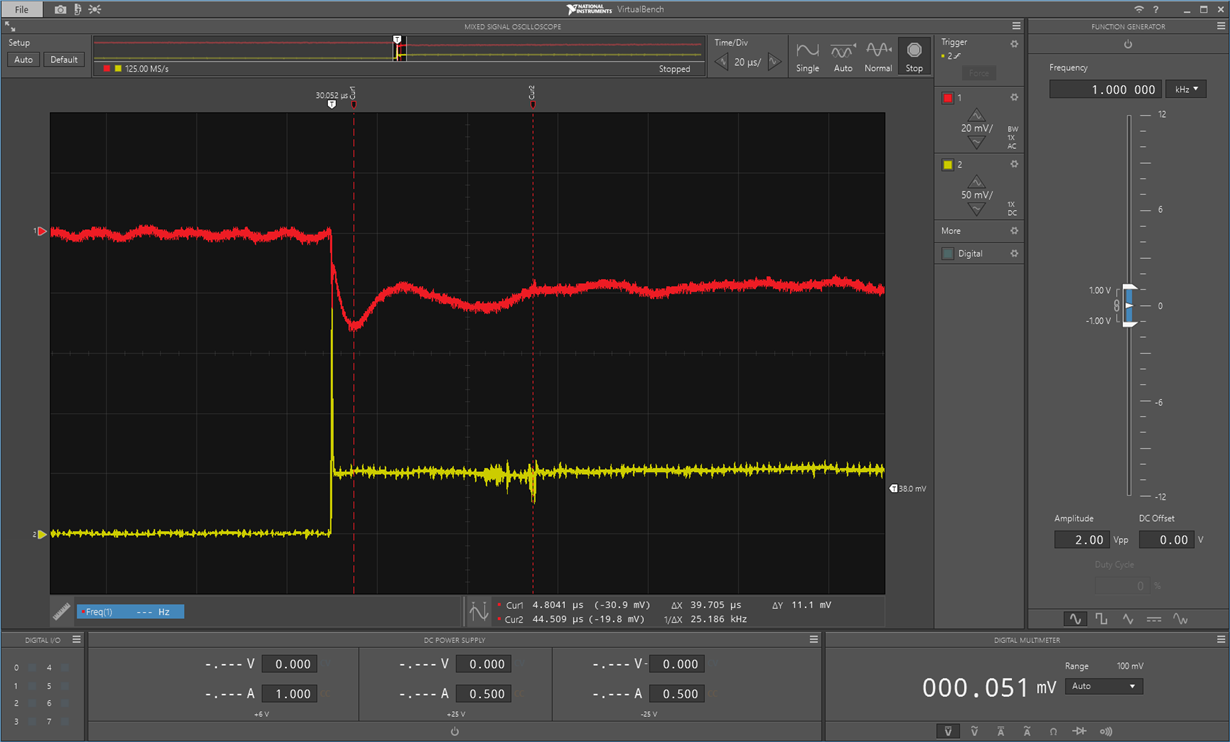

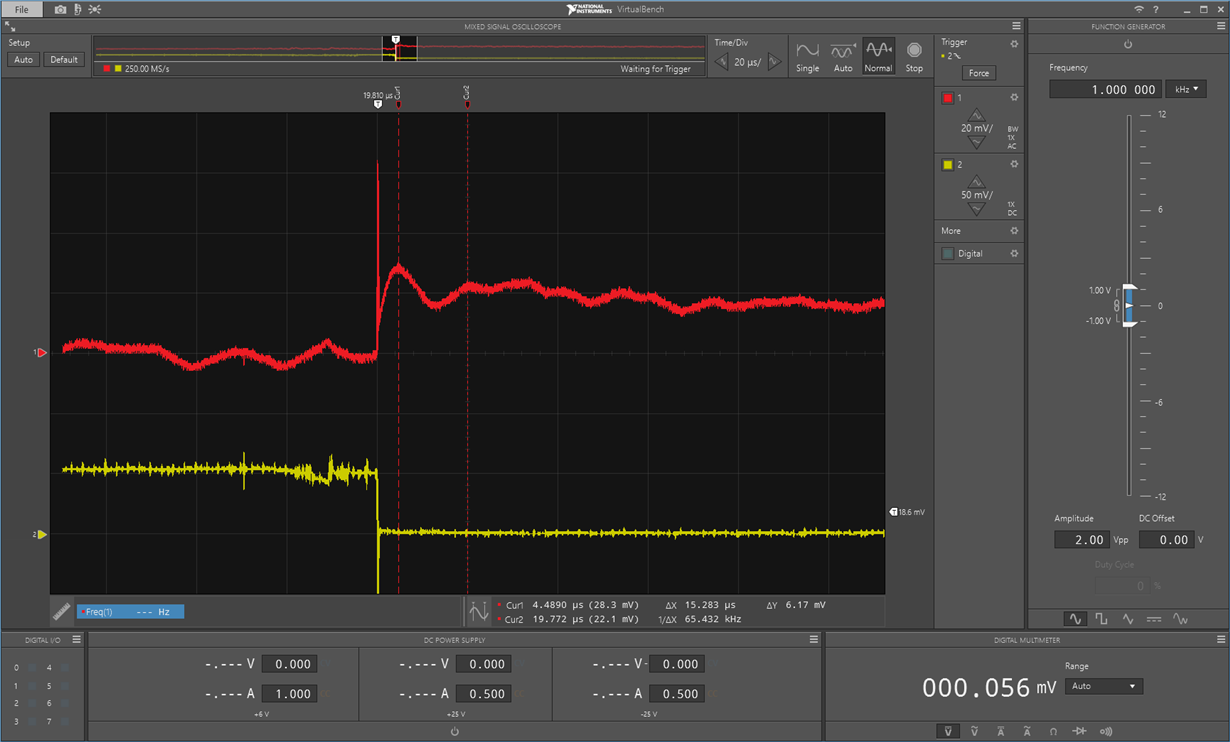

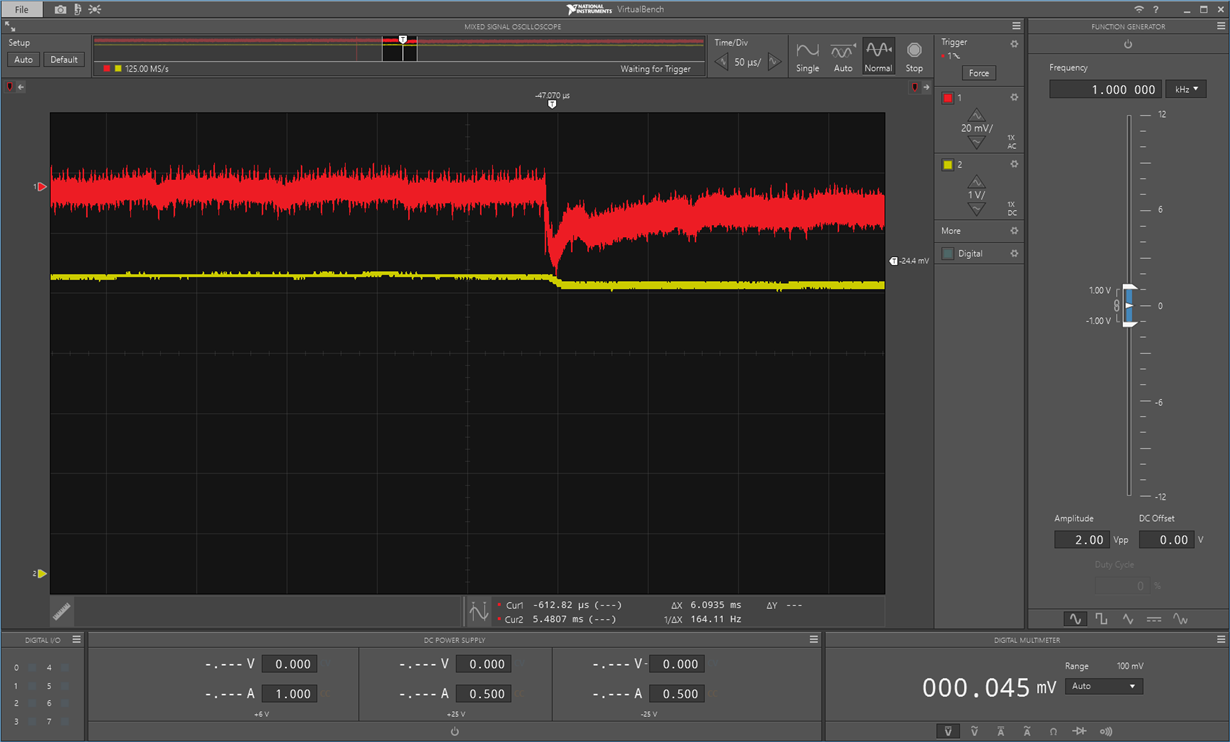

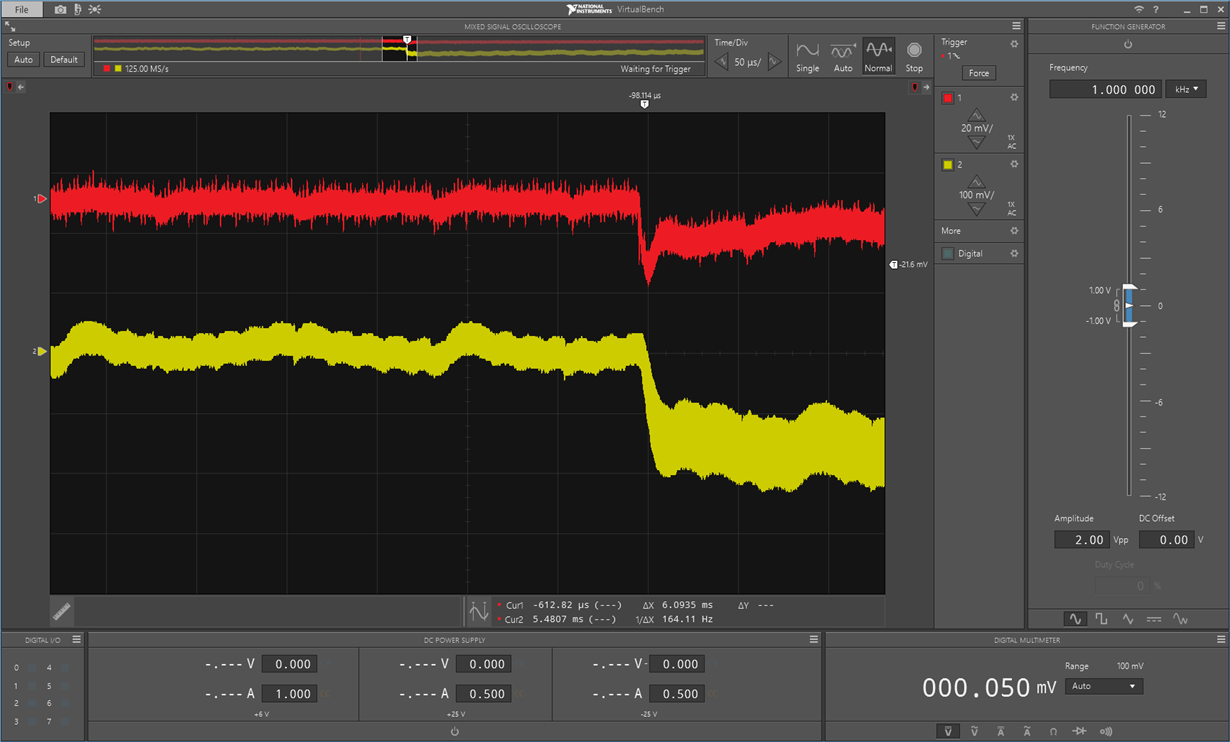

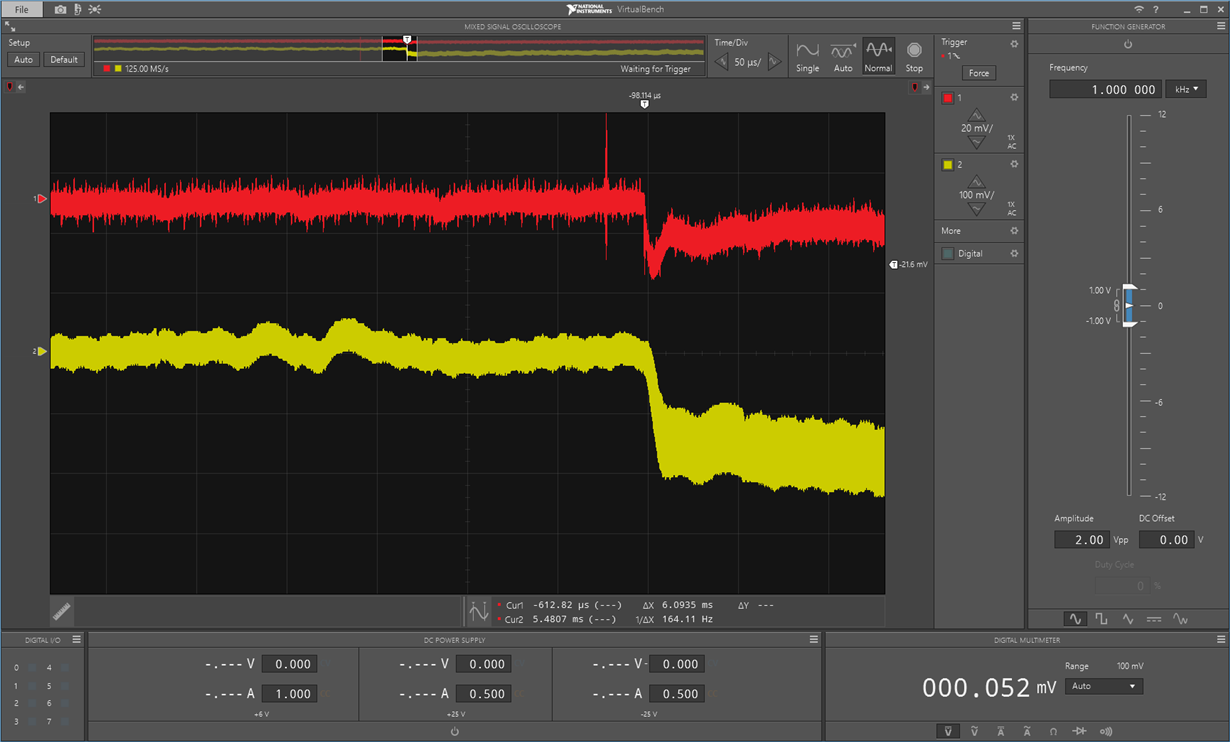

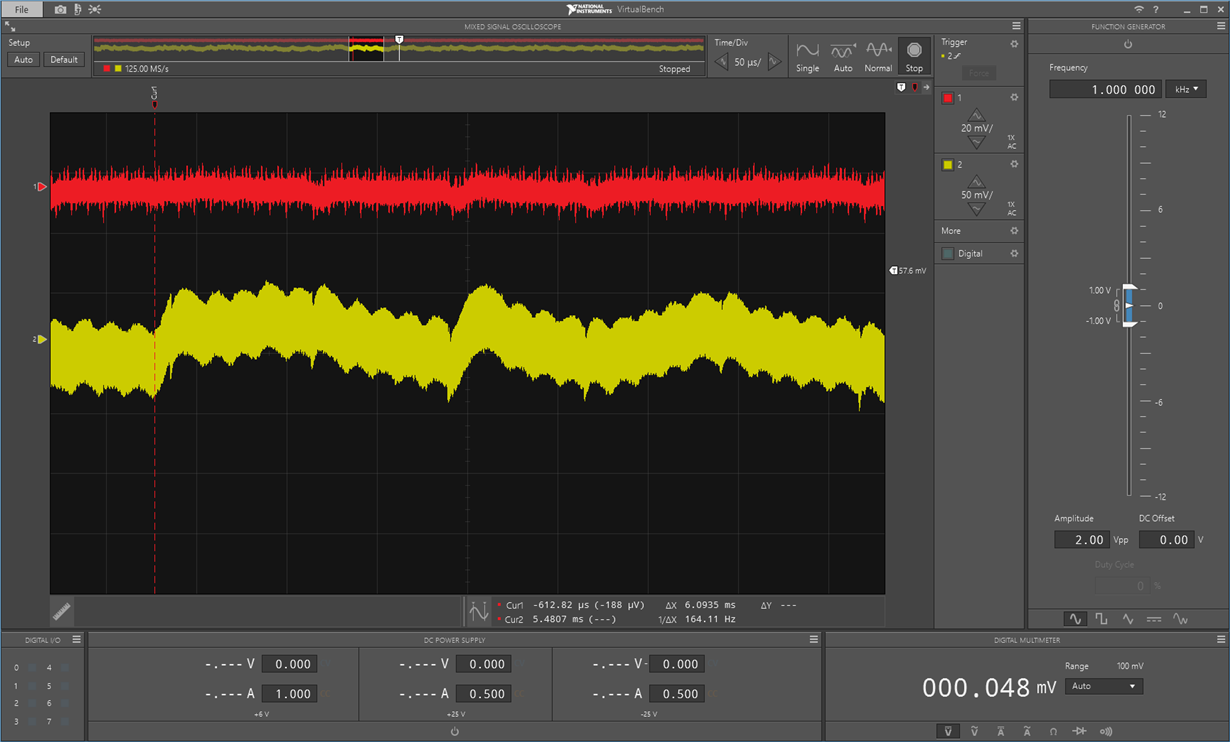

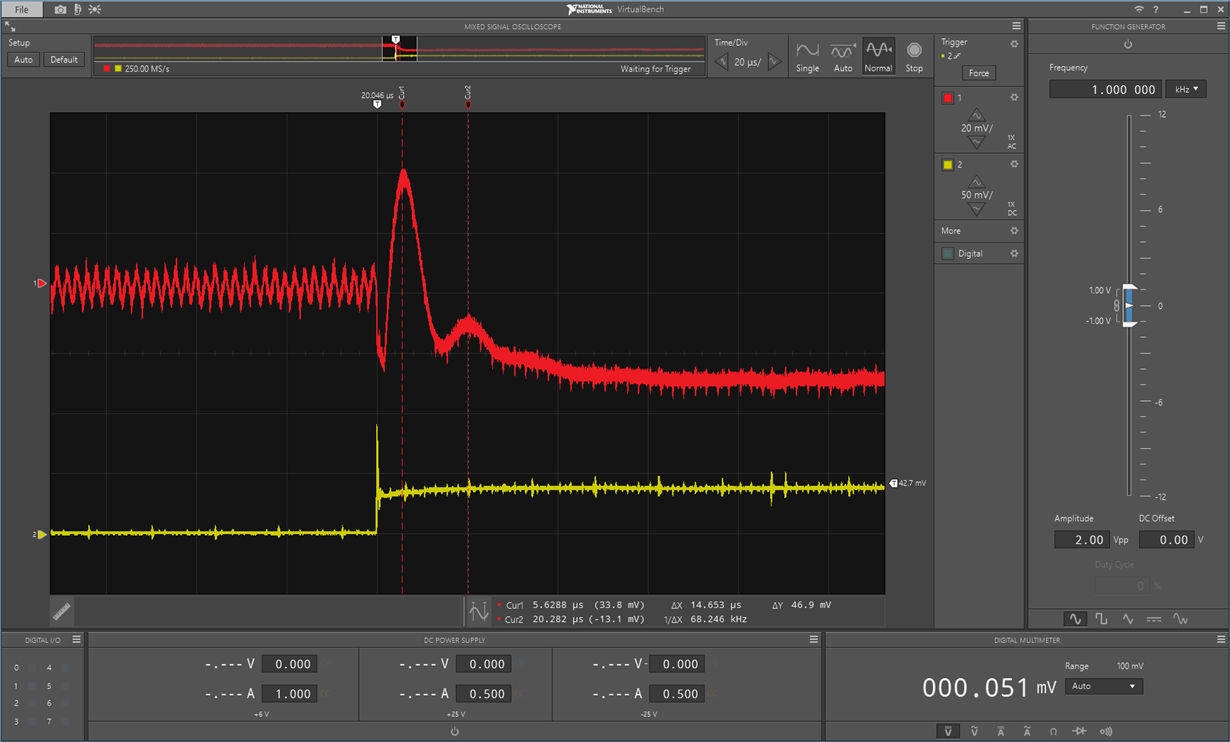

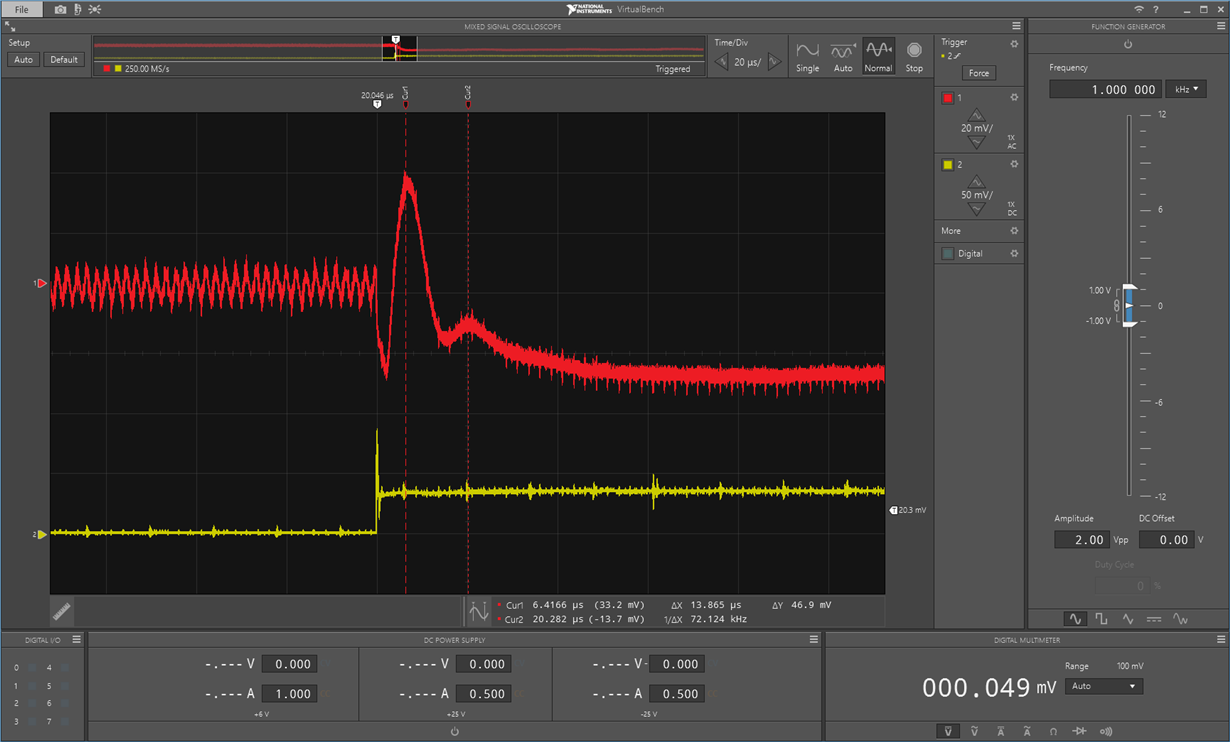

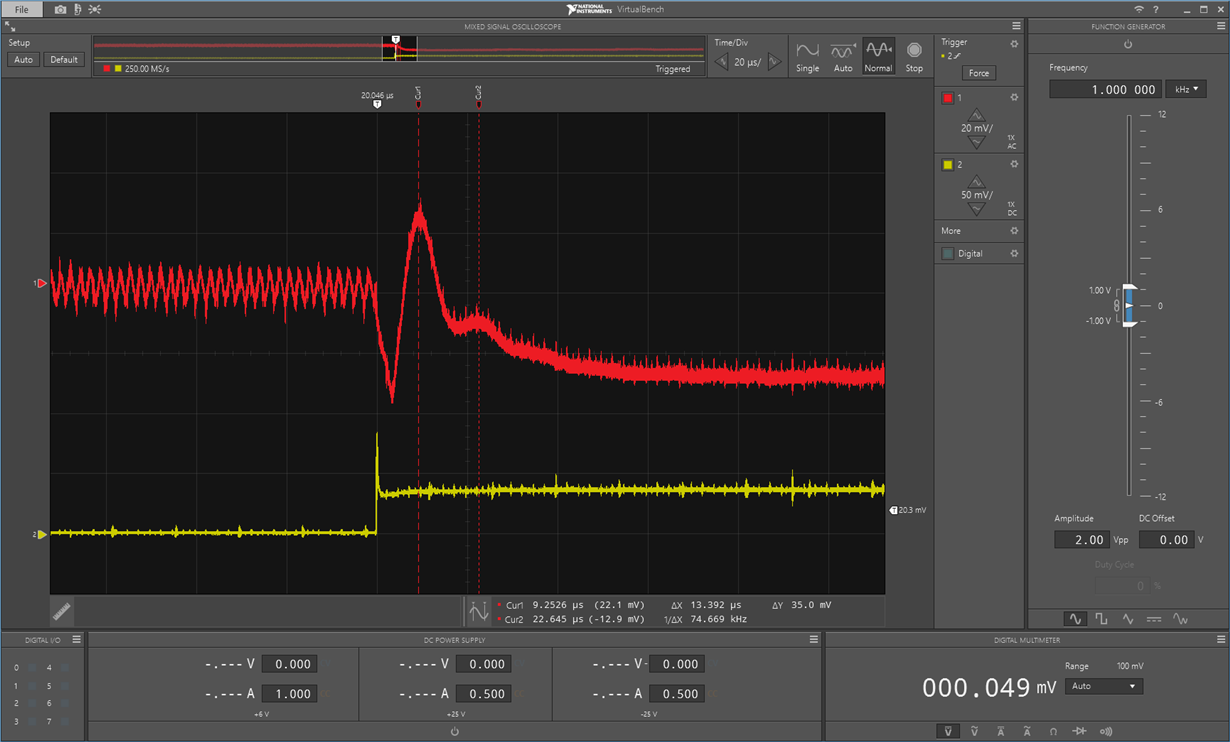

我尝试了不同的 CFF 来提高控制环路相位裕度、但通过更改 CFF 值似乎没有太大的改进空间。 我已阅读并遵循 TI 应用手册 SLVA289B、根据负载阶跃响应的测量值计算 CFF 值。 计算出的 CFF 约为68pF。 我尝试 了47pF ~ 330pF 范围内的不同值。 最好的一个( 就相位裕度而言)是 CFF = 82pF。 请参阅随附的示波器截图、了解负载从100mA 变为 400mA 时的阶跃响应。 根据阶跃响应波形、相位裕度约为30度、这仍然小于 控制环路无条件稳定所需的40度。

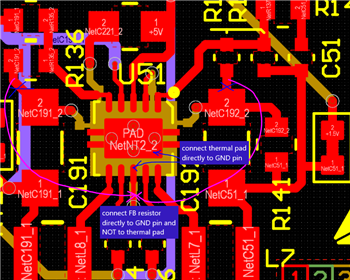

电路说明:我们的设计使用 TPS62410的转换器2生成1.5V 电压。 75k 欧姆和51.1k 欧姆电阻用作分压电阻以设置电压。 使用82pF 前馈电容器、该电容器与75k 电阻器并联。 此降压转换器使用2.2uH 电感器、而22uF 陶瓷电容器用作 Cout。 MODE/Data 引脚接地。 EN1和 EN2连接到+5V 输入电压。 Cin 是 一个10uF 陶瓷电容器。

问题/请求:

1. 请告知我如何改进控制环路相补角。

2、最大值是多少 ADJ2引脚上的泄漏电流? 我在数据表中找不到它。 但是、数据表显示 DEV_1的最大泄漏电流为1uA、我假设最大泄漏电流为1uA ADJ2上的泄漏电流也为1uA。 如果我错了、请纠正我的问题。 基于此假设、由于 此泄漏电流导致的输出电压误差、因此无法在数据表中的建议范围内选择这些分压电阻器的电阻。