请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS54240 我确认 TPS54240上的外部时钟电路、请让我确认下面两点;

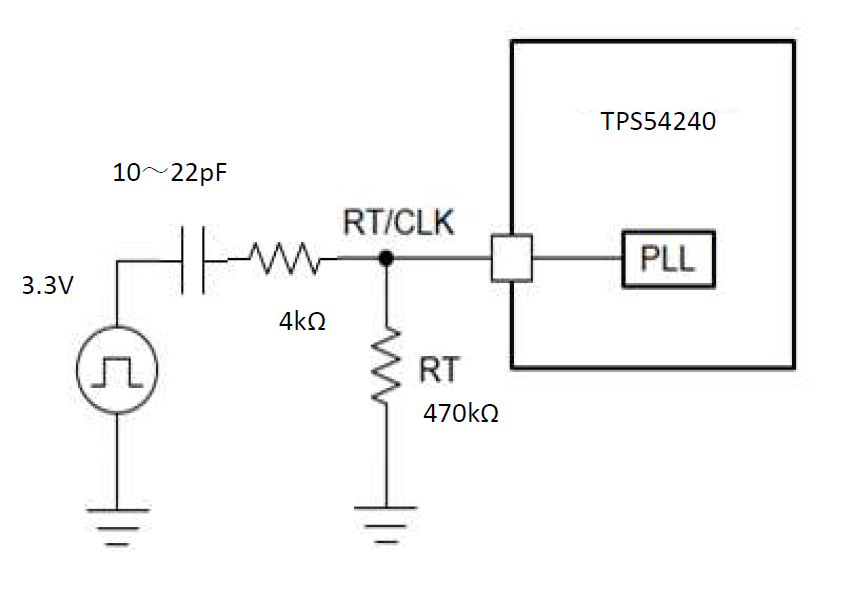

・下面附上了电路图像、这没问题吗?

我对 RT/CLK 引脚电压几乎不担心、10pF 耦合会发生负电压或不发生负电压。

・是否有几个 TPS54240使用一个时钟源、没问题? (例如、Clock⇒TPS54240的 RT/CLK×3)

在这种情况下、对于少数 TPS54240、是否有可能成为并联 RT 电阻器值和奇怪的开关频率?

此致、

Satoshi