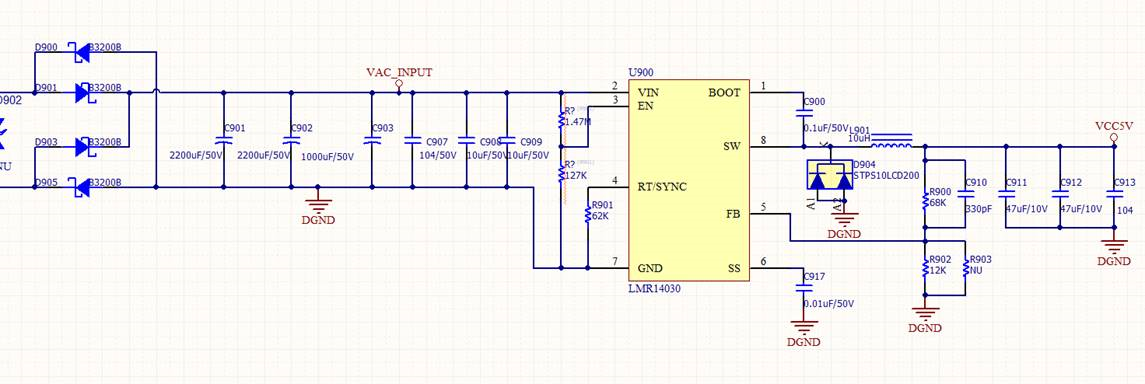

主题中讨论的其他器件: LMR14030

我们发现、当使用 LMR16030时、在断电期间输出电压异常。 但是、当使用 LMR14030的 P2P 器件时、断电期间不会出现问题。 您能否帮助检查原理图上是否缺少任何内容! 尤其是、请检查用于 EN 引脚控制的分压电阻是否正常?

备注:在客户设计中、全波形整流器的输入纹波电容为5500uF。

条件:VIN:24V、Vout:5V、Iout:1.5A

***原理图是 WEBENCH 设计的后续操作。

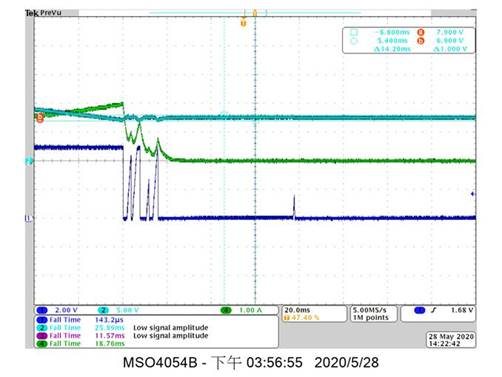

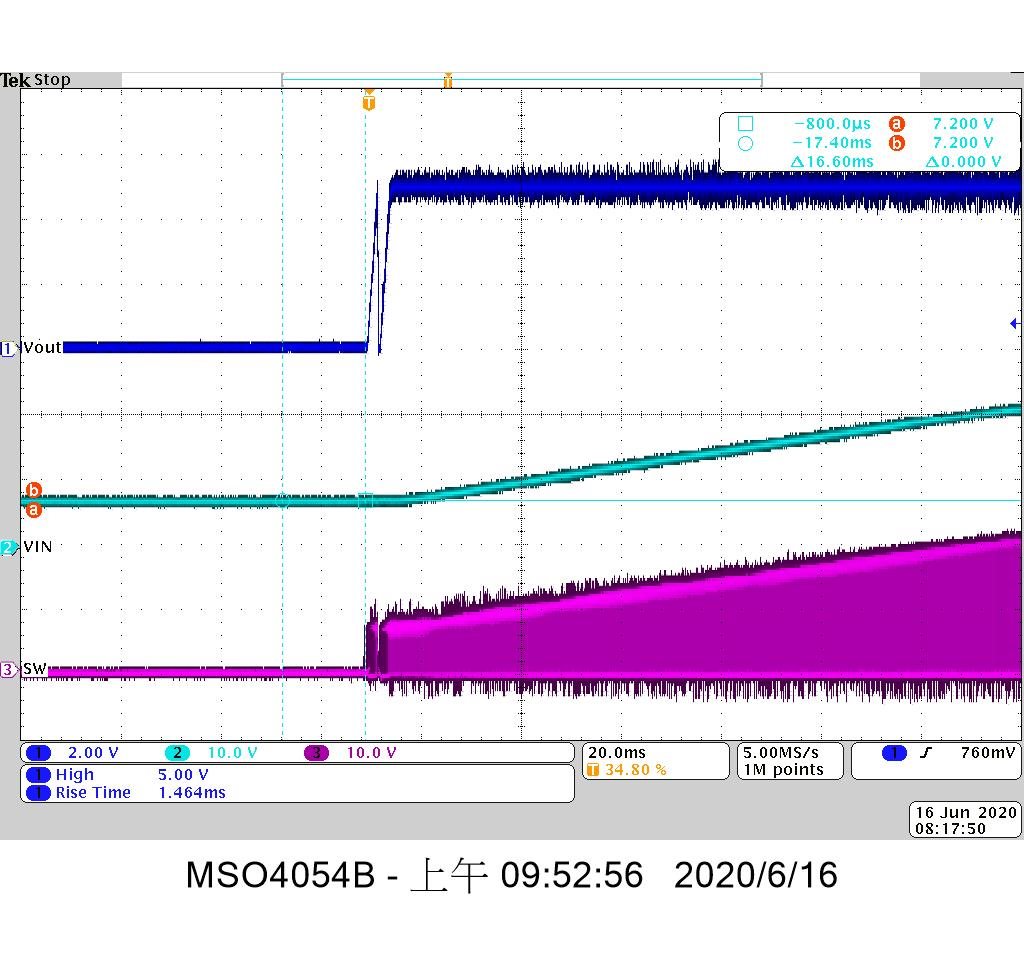

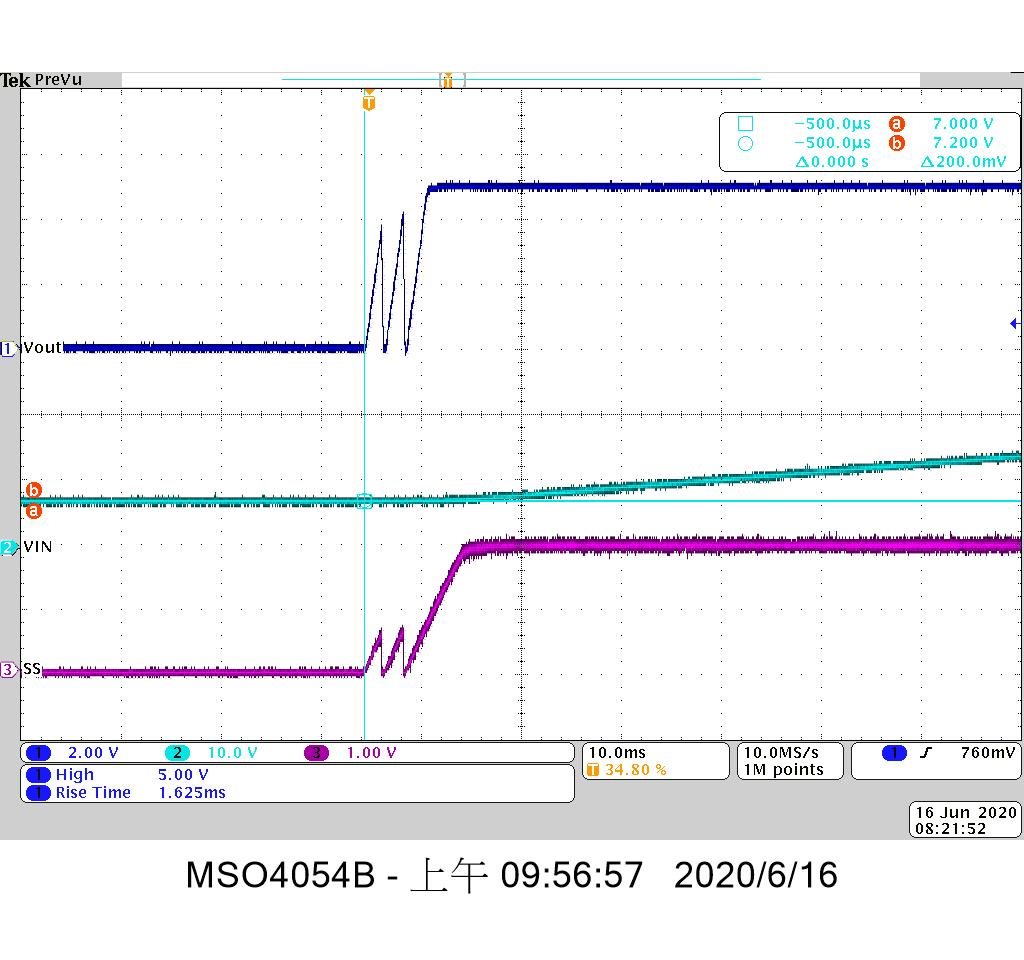

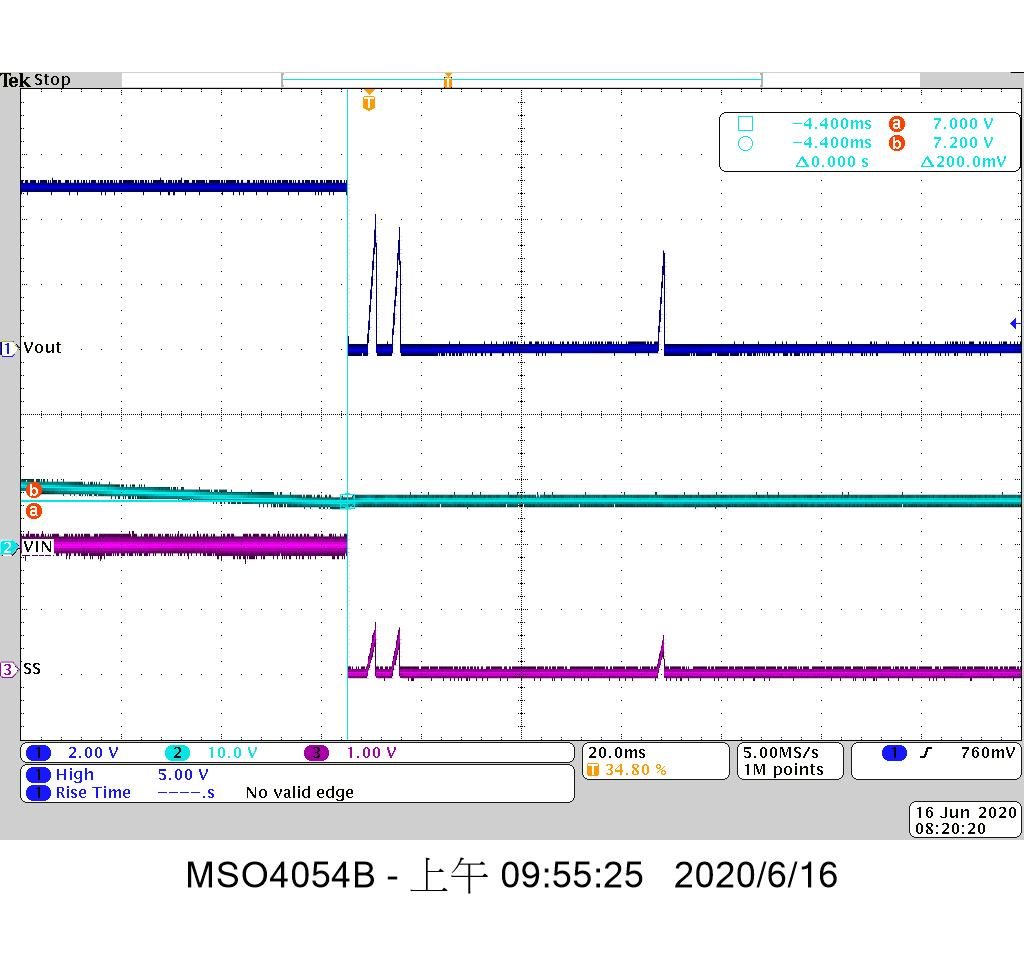

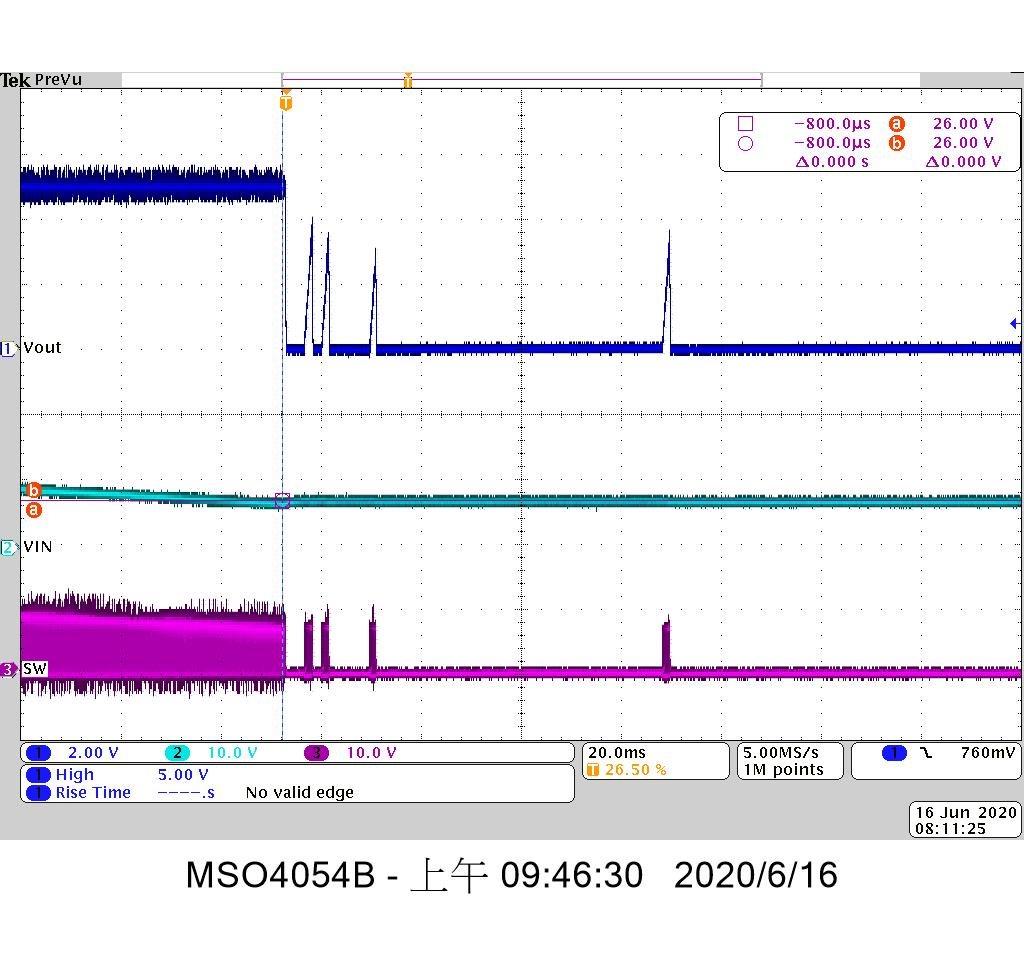

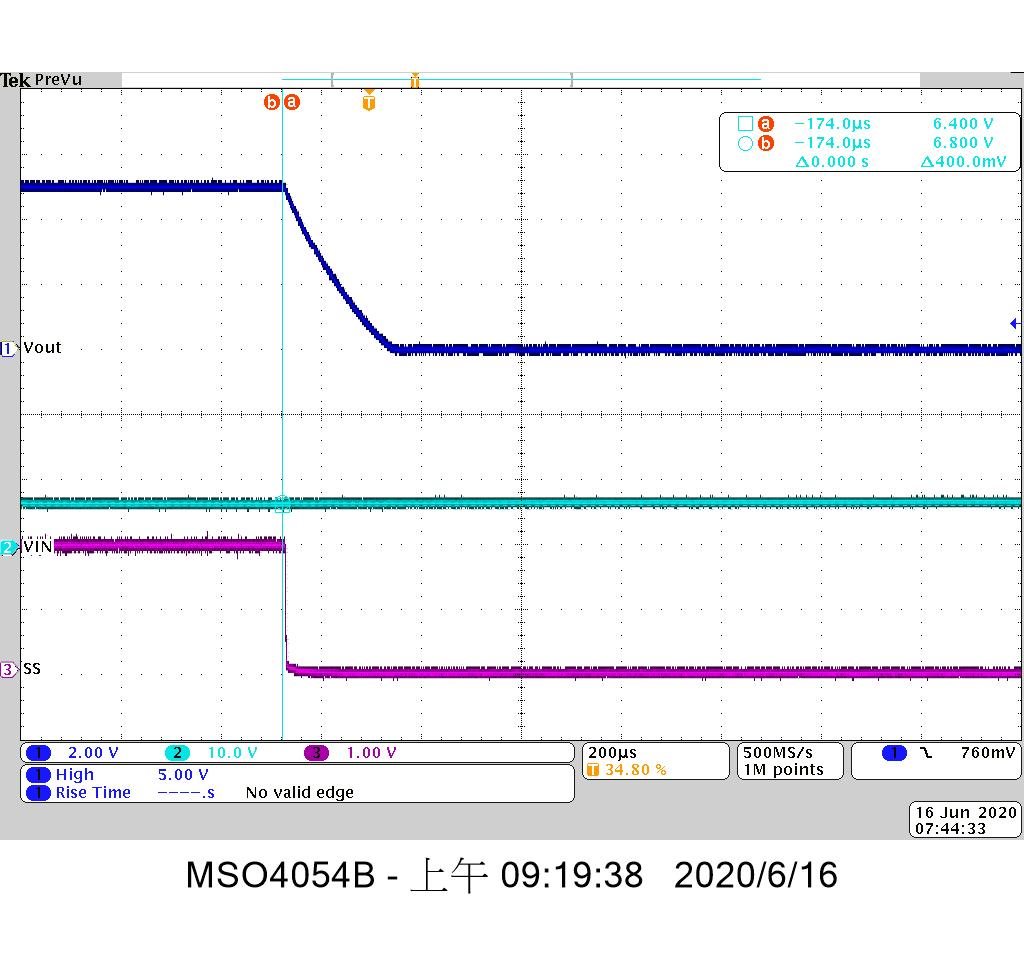

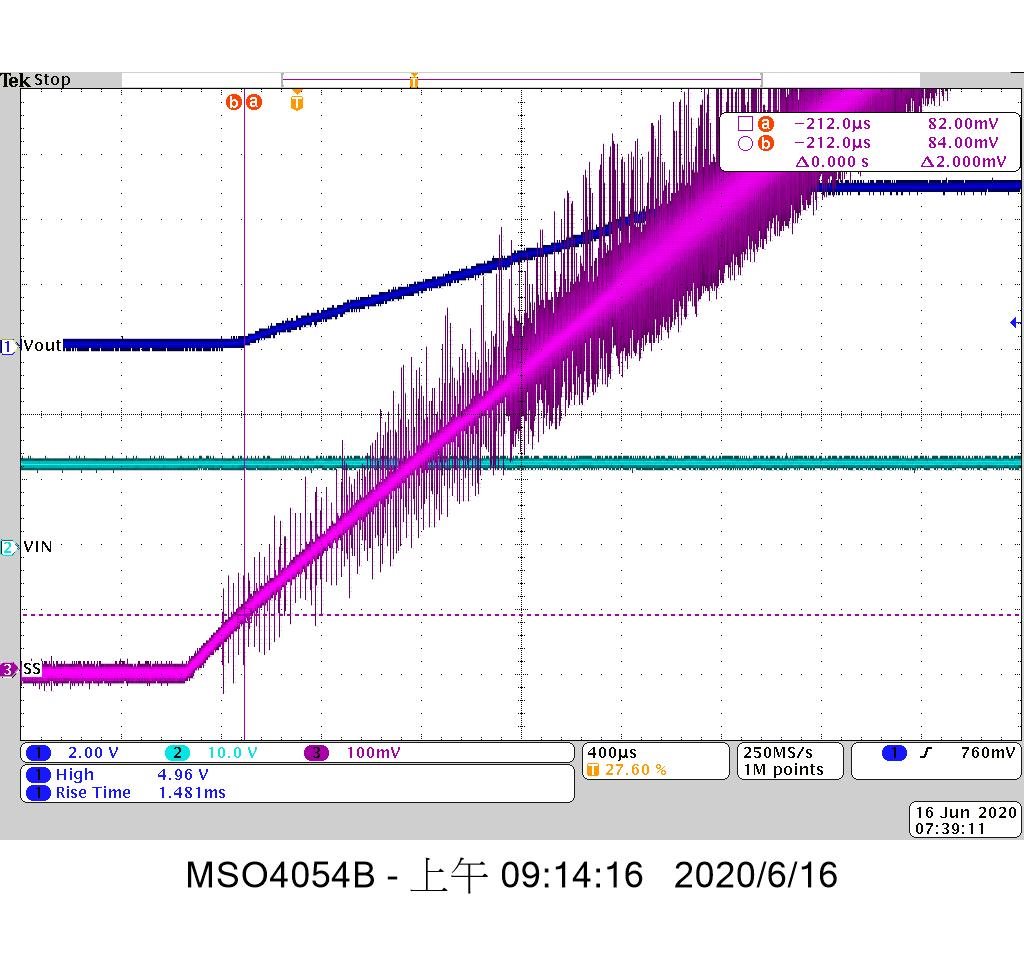

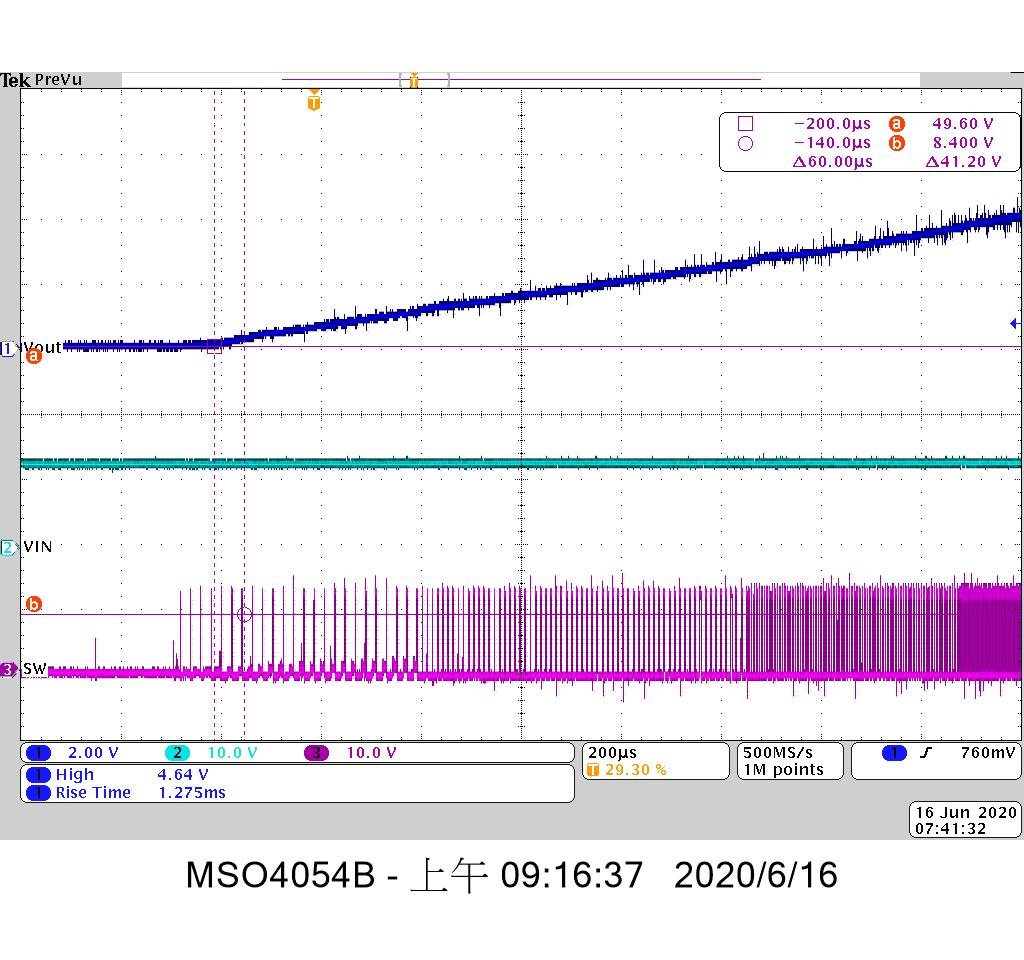

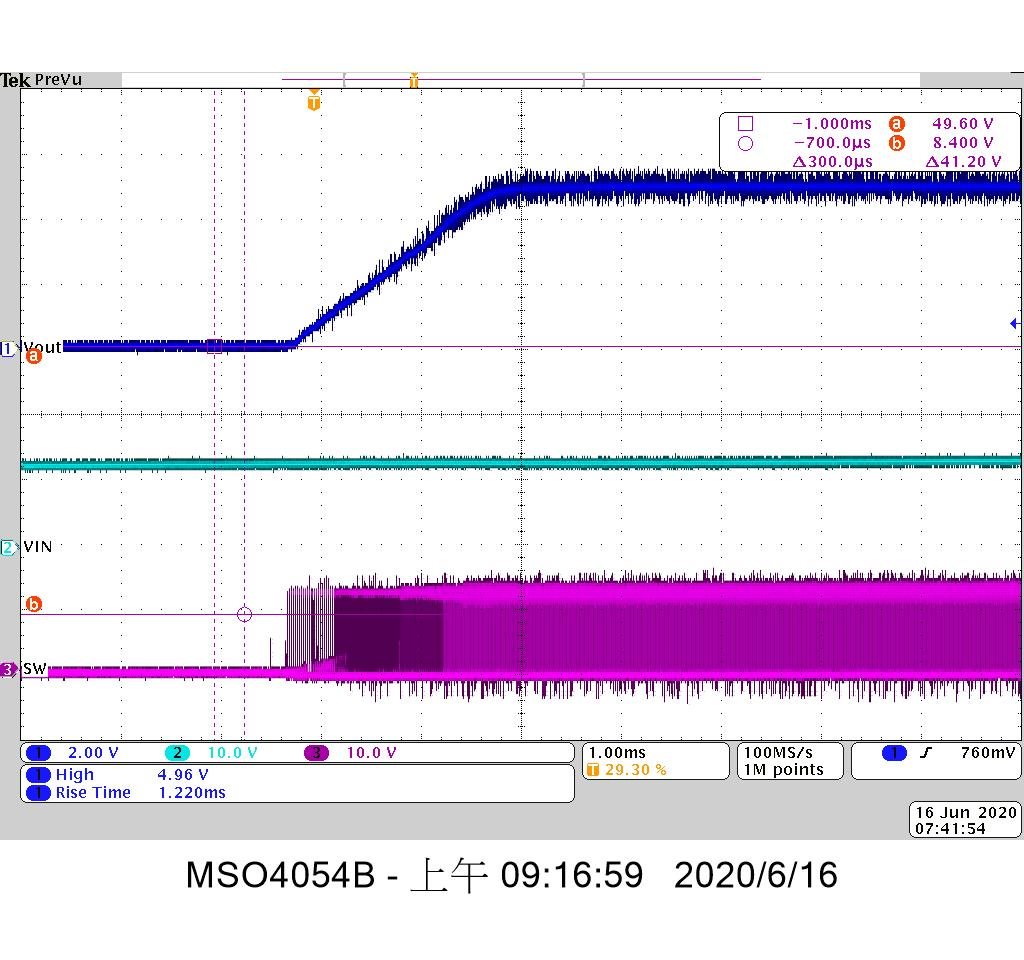

LMR16030的测试结果: CH1 VOUT 5V、CH2 VIN 24V、CH4输入电流

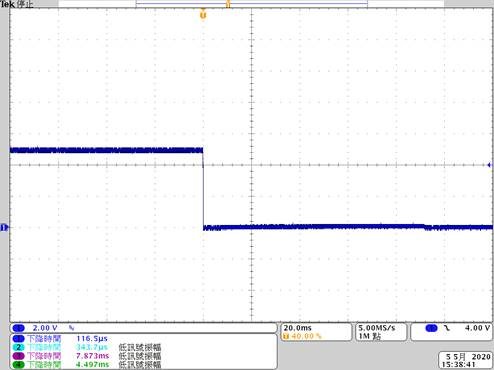

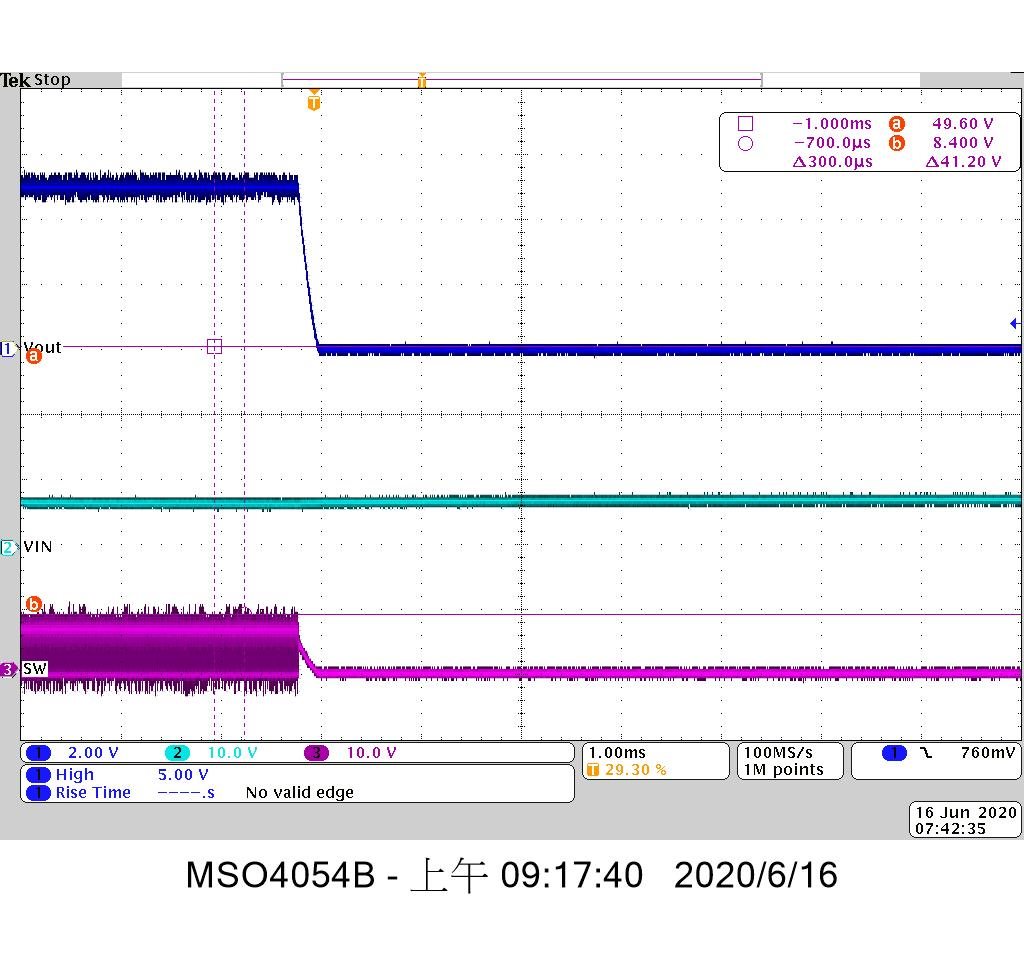

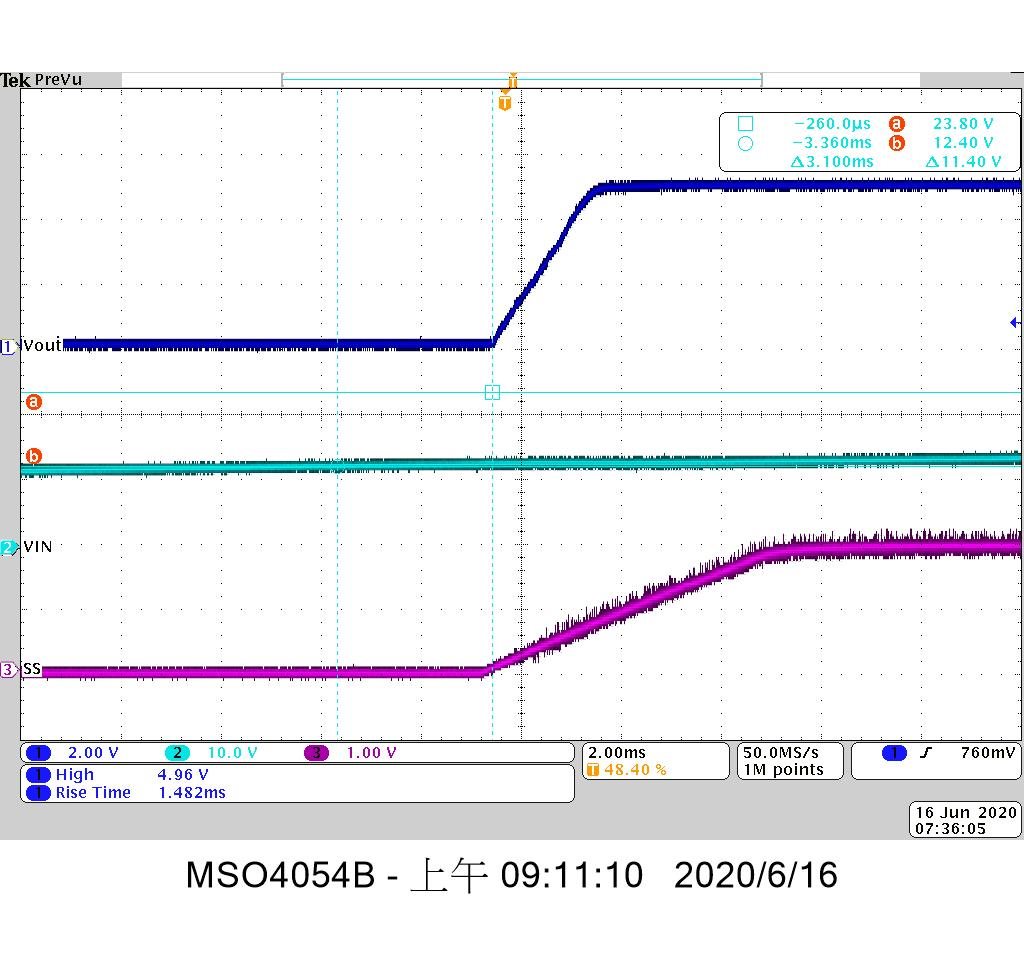

2. 通道1 VOUT 5V (LMR14030)