各位专家、您好!

我将使用 GaN 开关设计 VSI。 我的问题在于 PCB 布局。 如 EPC 和 GaN 系统白皮书所述、最佳布局实践是使用4层电路板、VDC+使用顶层、PGND 使用中间层1。 这样、电源环路仅跨越顶部和中间层1。 由于两层之间的距离为8mil、因此与传统的横向和垂直环路相比、会有强大的自场消除功能、从而显著降低环路电感。

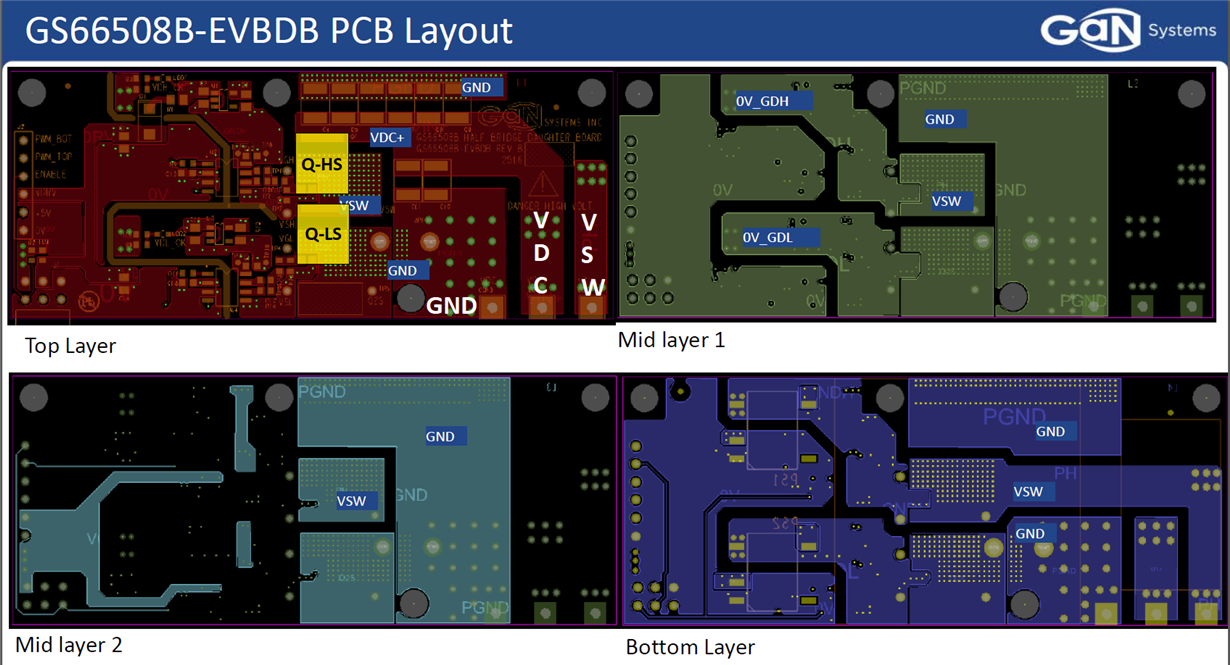

但是、我遇到了一个看起来相当奇怪的 GaN 系统设计。 这是4层设计。 我将 GaN 开关突出显示为黄色框

此设计使用 VDC+顶层。 中间层1用作 PGND。 但除此之外、中间层2也用作 PGND。 此外、顶层还有2个直流链路电容器、构成了一个横向电源环路。 因此、这意味着、此设计并行使用3个电源环路(顶部横向、顶部中间1垂直和顶部中间2垂直)

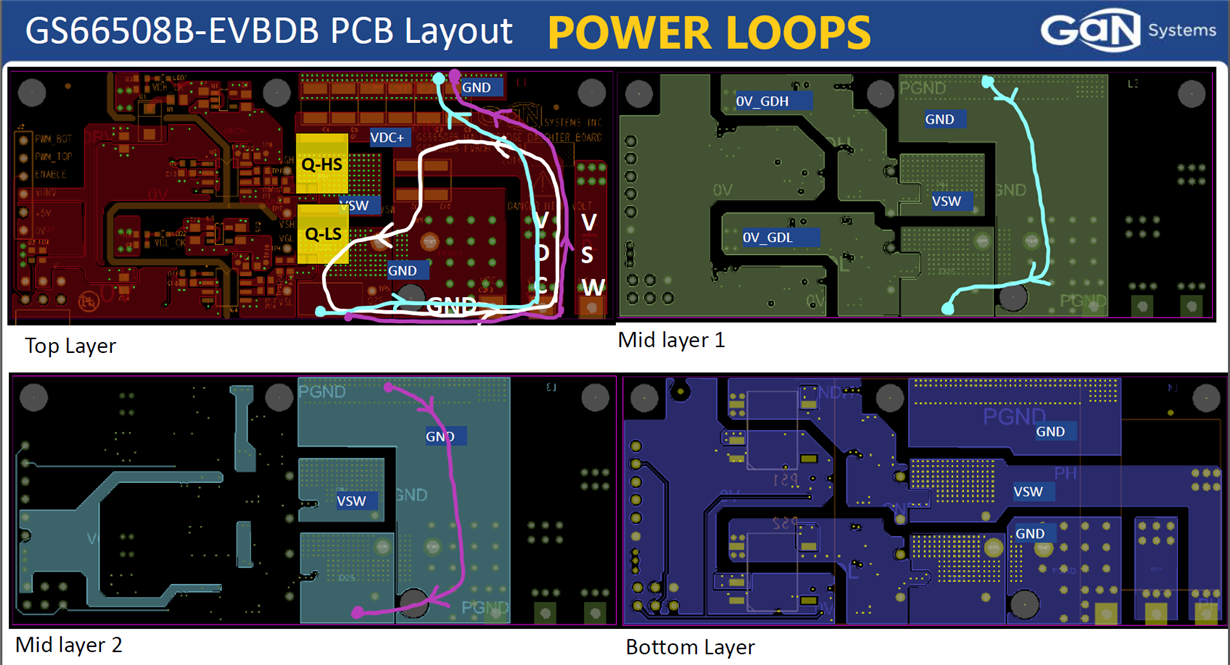

我将附上一张图片、以突出显示3个电源环路

白色->顶部横向回路

蓝色->顶部中间1垂直回路

粉红色->顶部中间2垂直环

由于3个环路具有不同的电感 L1、L2、L3、因此有效电源环路电感 LP 将为 L1 || L2 || L3。 这意味着电感 LP 将低于 L1、L2、L3的最小值。

但是、如果从磁通量的角度观察、这似乎是反直觉的。 所有3个环路将产生通量、该通量将"建设性地"累加、因此、有效电源环路将具有大于最小电感环路(上-中1)产生的通量。 因此、从磁通角度来看、LP 将大于 L1、L2、L3的最小值

这里发生什么事了? 为什么在该设计中使用多条 GND 返回路径? 为电源环路使用多条返回路径是否合适?(忽略并联路径所提供的电阻降低情况)。

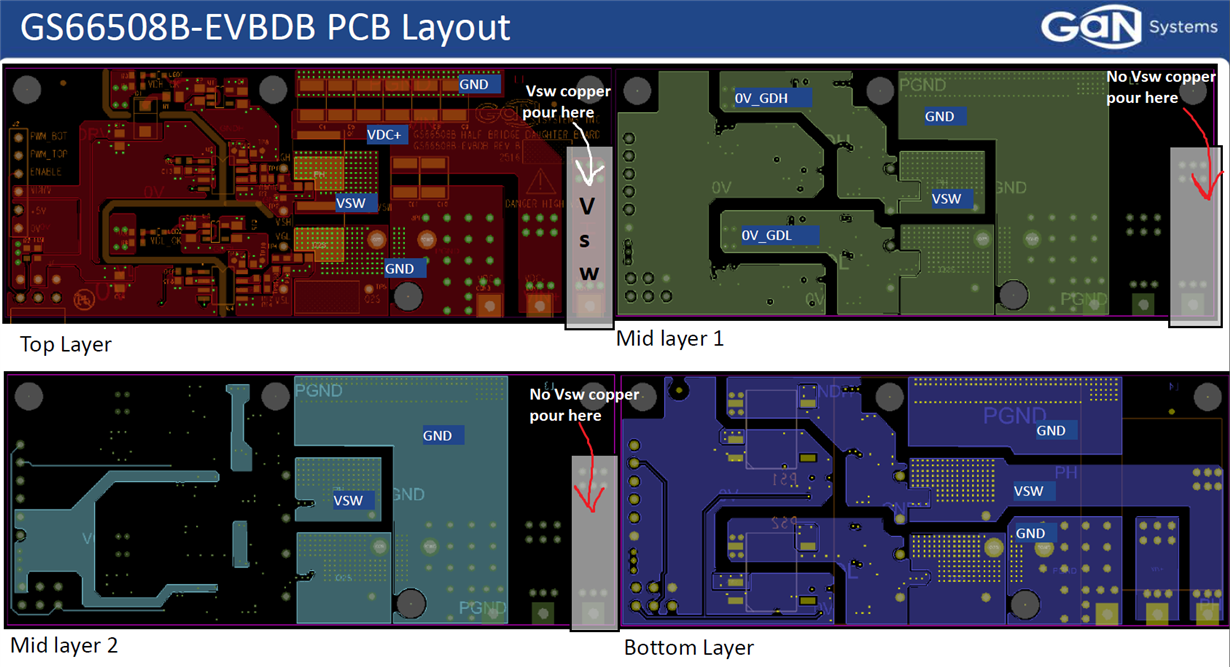

此外、布线 VSW 和 VDC 仅在顶层和底层上进行扩展。 它们本来可以将 VDC 和 VSW 覆铜放在中间层1和中间层2上、但实际上没有。 为什么?