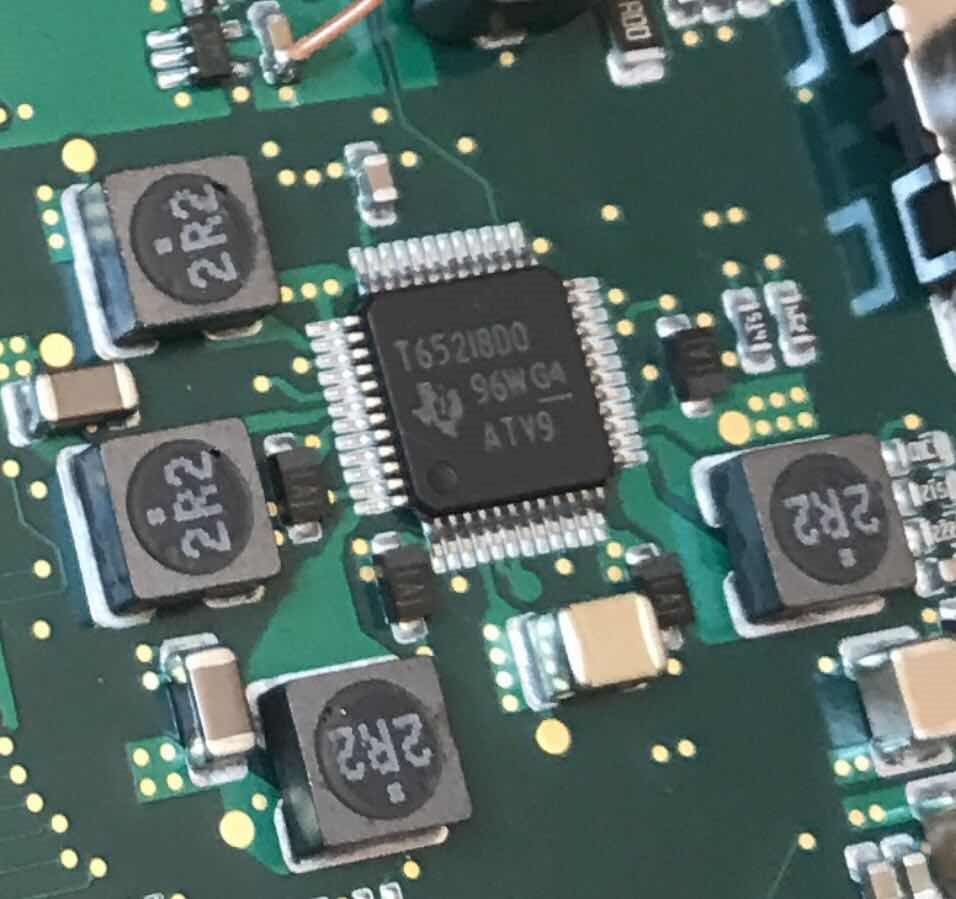

主题中讨论的其他器件:AM3358、 TPS65218、 TPS51200

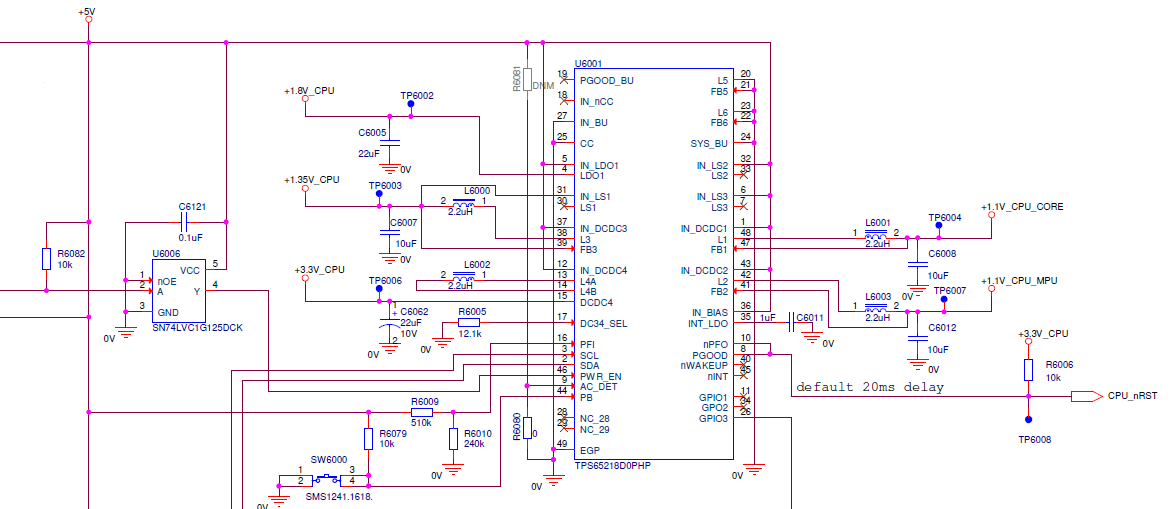

我们将 TPS65218D0连接到 AM3358。 该板还具有一些连接到其他 PM 部件的 Cyclone 10 FPGA。

FPGA I/O (+3.3V)由 LM20143MHE 生成。

该器件的 PGOOD 信号使用引脚46 PWR_EN 启用 TPS65218。

因此、在电源序列中、FPGA I/O 首先打开。

我们有10块板。 当+3.3V 电压打开时、其中9个发生故障。

我们在更改电源后可以使用的最后一个板。

我们发现电路板从5V 汲取0.6A 电流。

我们已经尝试在其他电路板上使用四种不同的电源、但它们无法正常启动。

我们不使用 DCDC5 & 6或 GPIO1

我们在 DCDC4上看到大约2.2V 的电压、我们怀疑 FPGA I/O 驱动 CPU I/O

它为3.3-2.2 = 1.1或几乎为两个二极管压降。

原理图。

电容为22uF、基于 http://e2e.ti.com/support/power-management/f/196/t/844935

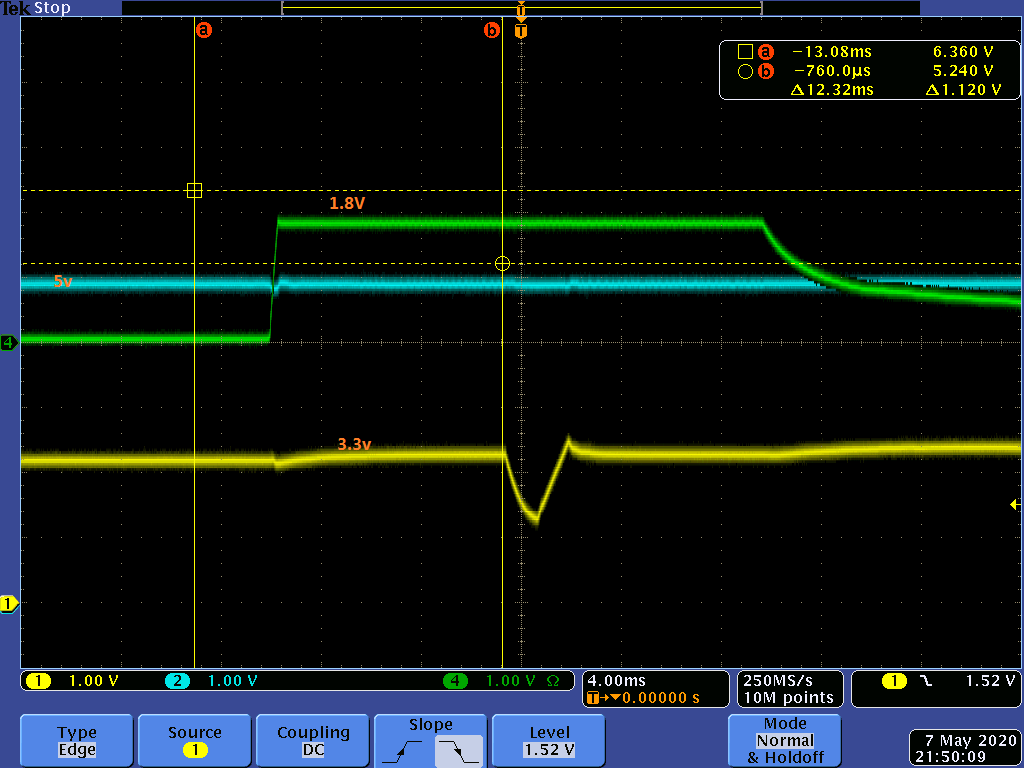

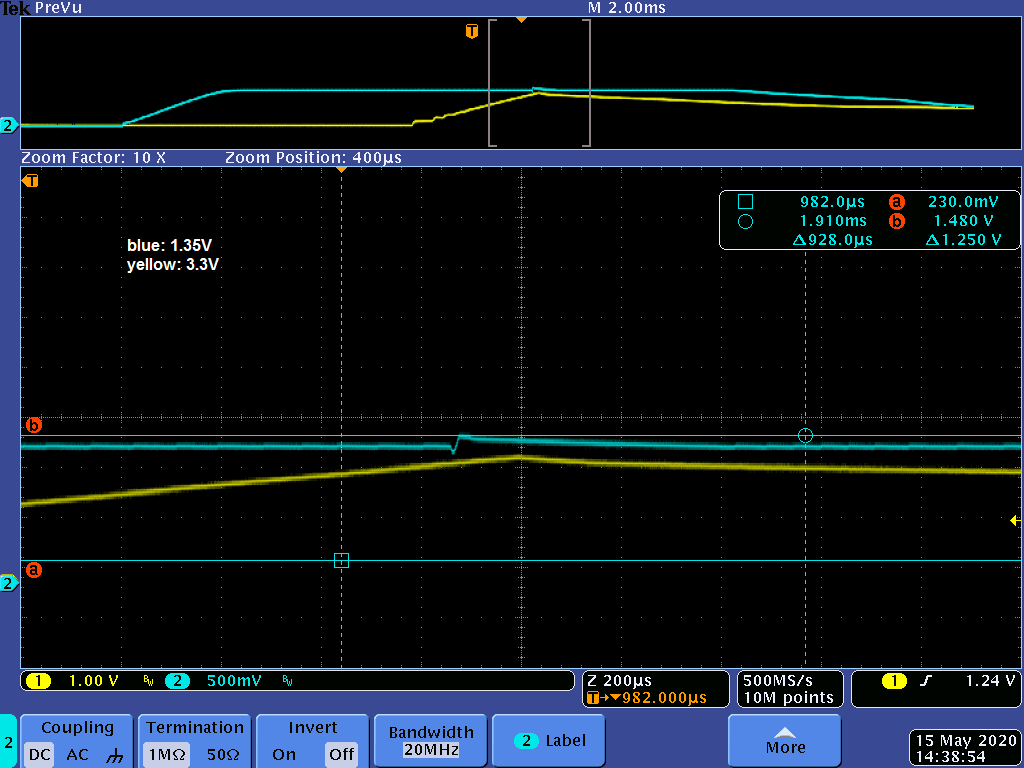

1.8V 首先打开。 发生这种情况时、5V 电源中的压降最小。

然后、1.35V 会在该电压之后导通。 这似乎也起作用、在2ms 内达到其电压。

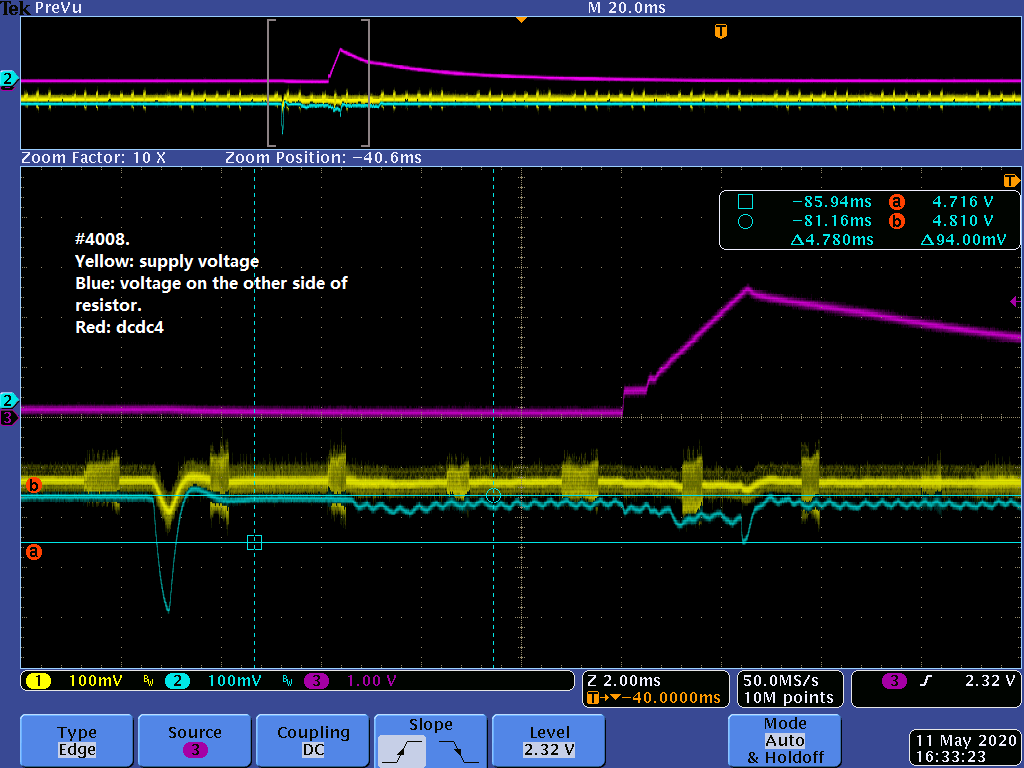

3.3V 具有~2.2V 的值、然后开始*下降* 0.6V、 +1.35V 达到其值后5ms、然后再次开始增加

然后关闭。

我们希望更好地了解电源序列时序。

序列应为...、DCDC3=1.35V、GPIO1、DCDC4=+3.3V、...

DCDC4 (+3.3V)应在 DCDC3 (+1.35V)之后启动 DLY5 + DLY6

DLY5 = DLY6 = 2ms、因此 DCDC4应在 DCDC3之后4ms 开始。

在下图中、我们看到 DCDC4在7/5*4ms 或5.6ms 后骤降、然后升至2.6V、直到10/5*4ms = 8ms。

这是启动后的2、4ms、这是在应自行关闭之前分配的5ms 时间之前。

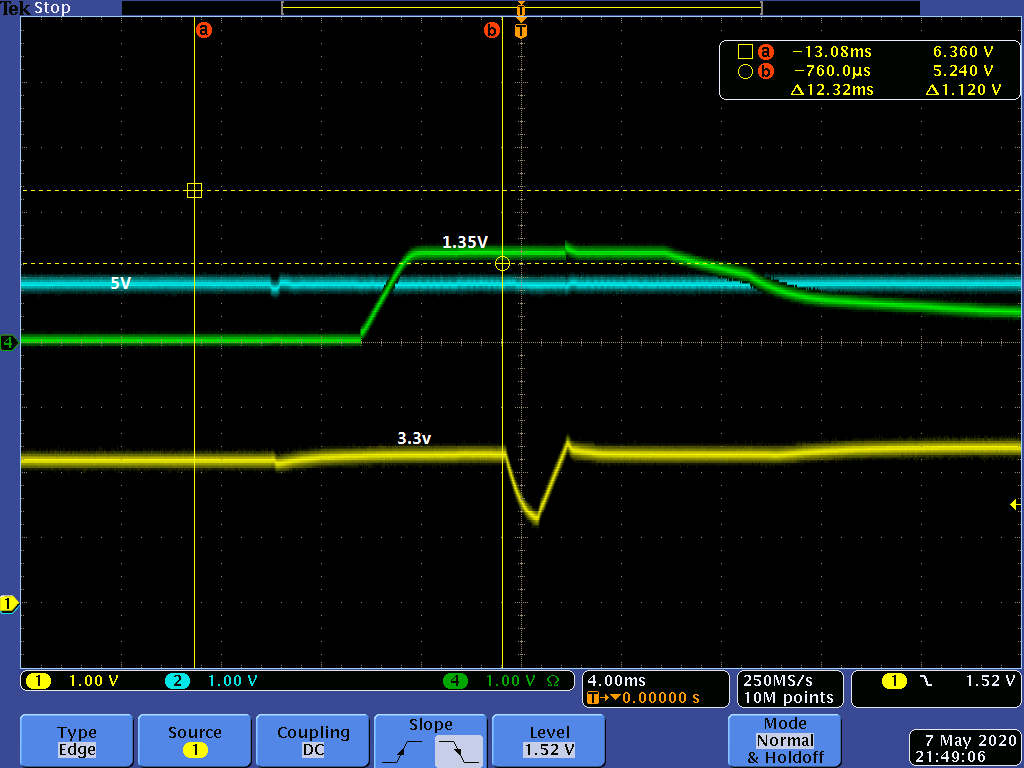

为了避免 FPGA 的干扰、我们关闭稳压器以了解这种情况。

3.3V 稳压器在1.35V (5.6ms)之后7/5*4ms 打开。

它在+1.35V 之后仍在10/5 * 4ms 或8ms 关闭、并且此时已达到2.6V。

我们有15个 I/O 引脚、这些引脚使用10k Ω 电阻上拉至 DCDC4。

LED 通过330欧姆串联电阻连接、但在该状态下通常处于关闭状态。

有大约60uF 的去耦电容器。 CPU 周围最多(5 x 10uF)

的 VCC

4个单栅极

1个 SPI 闪存

1个 NAND 闪存

1个时钟缓冲器

1个用于 DDR3电压的 TPS51200BCT

1个 TMUX1574PW 模拟多路复用器。

2个 SDRA05-4R2 USB 保护电路。

似乎不会使 DCDC4过载。

有什么想法吗?