主题中讨论的其他器件: UCC2897A、 UCC28951、 PMP9656

大家好、

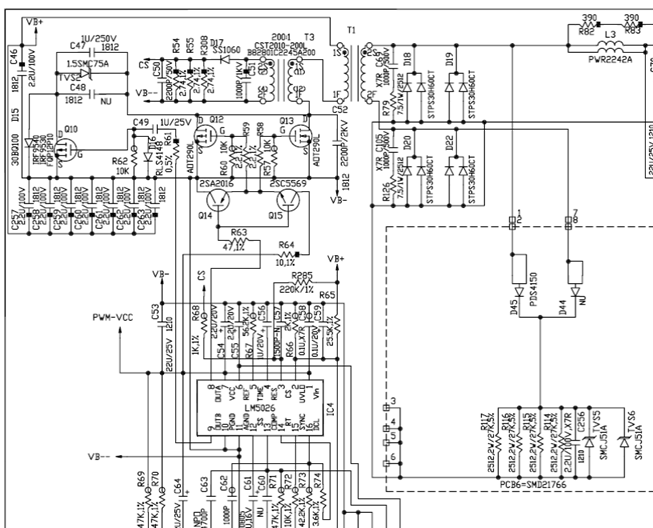

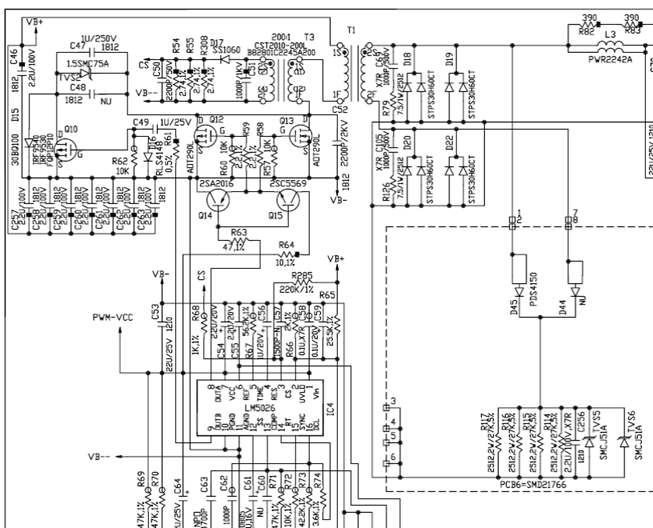

客户目前使用 LM5026提供300W、18~36V 输入、12V/25A 输出。

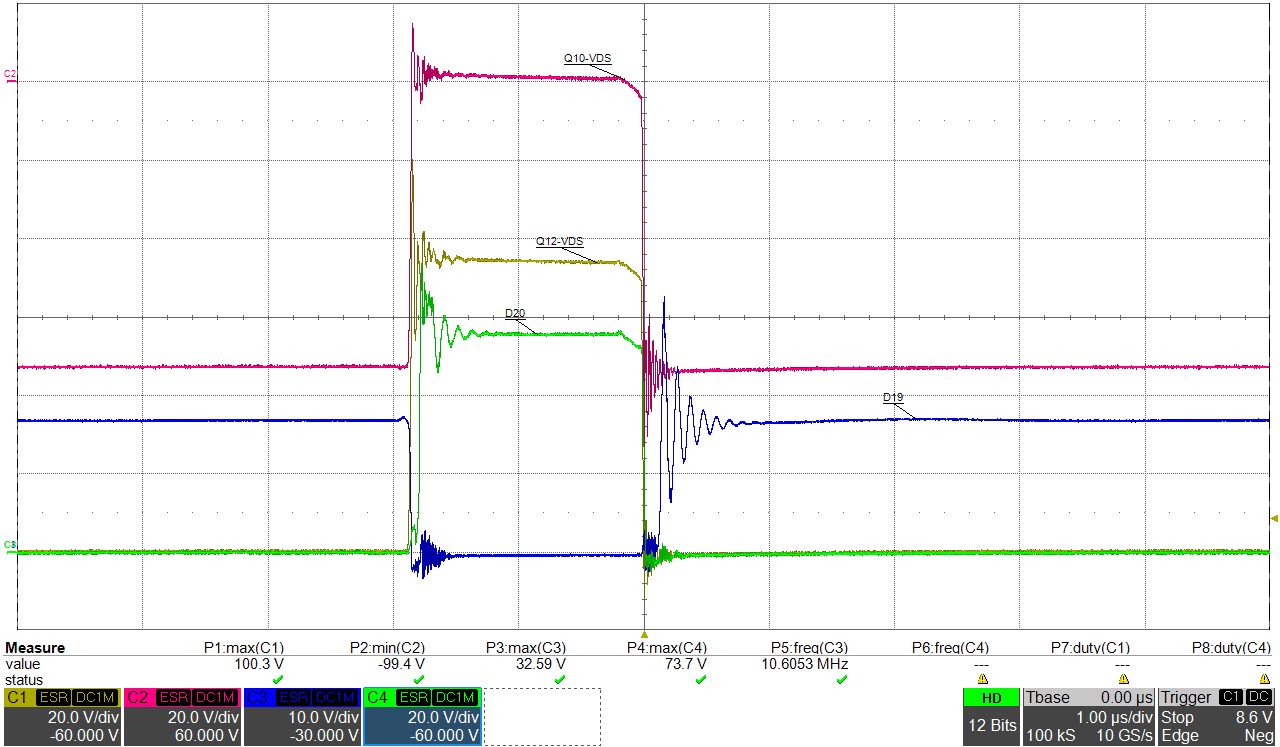

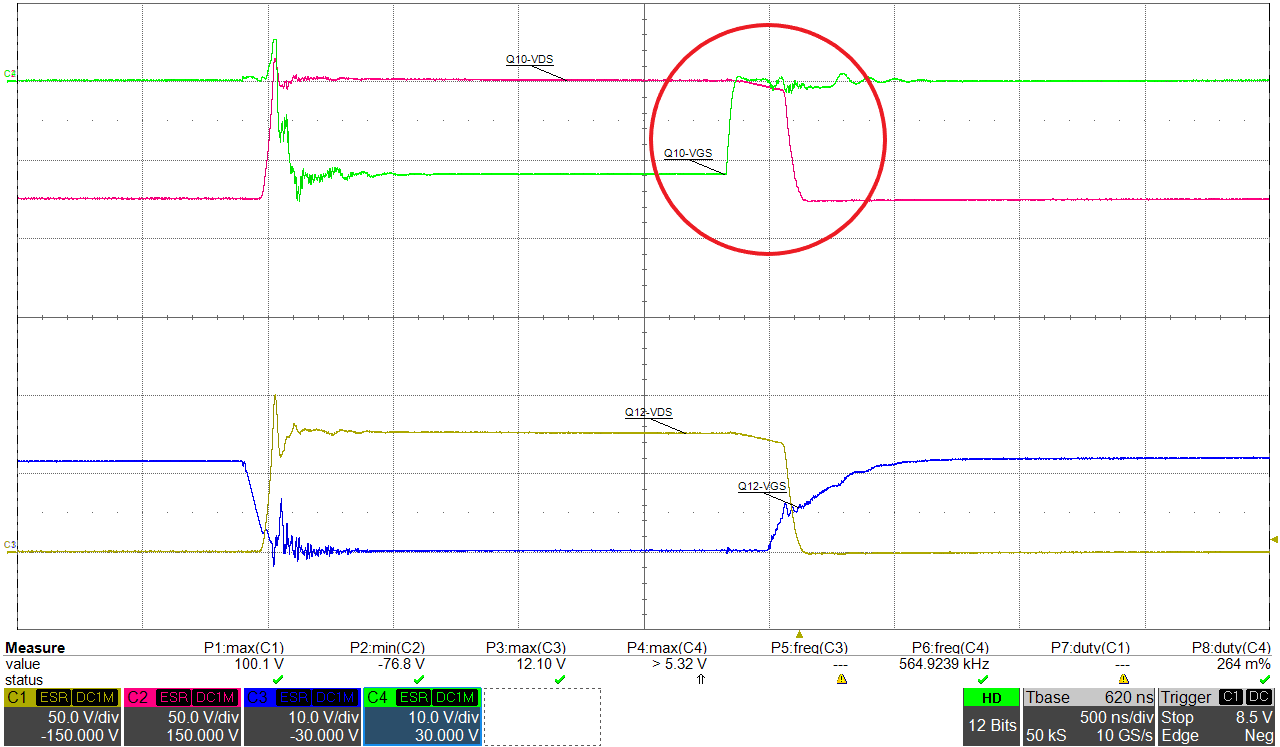

随着输出功率的增加、满载时可以发现 N MOSFET 和 P MOSFET 在导通时重叠、并且输出二极管的死区时间也过长。

最大占空比约为78%。 客户已调整时间引脚参数和变压器匝数、但仍无法改善。

客户已确认 ADI 的解决方案不会导致此问题。

之后、将有500W 应用。 此问题是否有任何解决方案? 谢谢。

此致

摇滚