主题中讨论的其他器件:TPS65218、 TIDA-00606

您好!

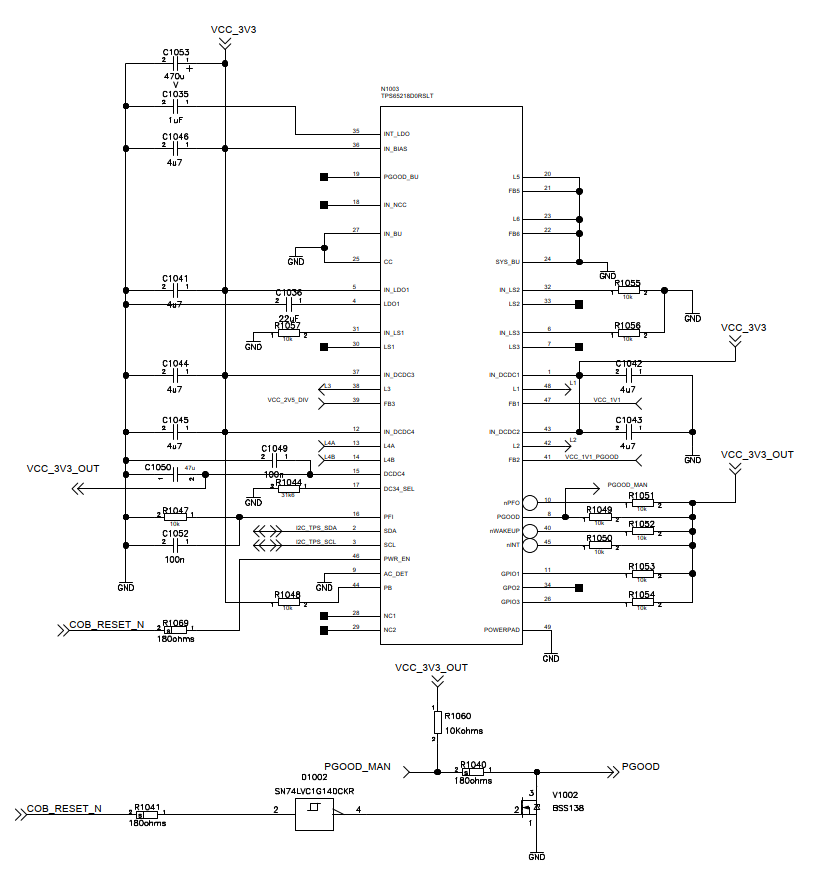

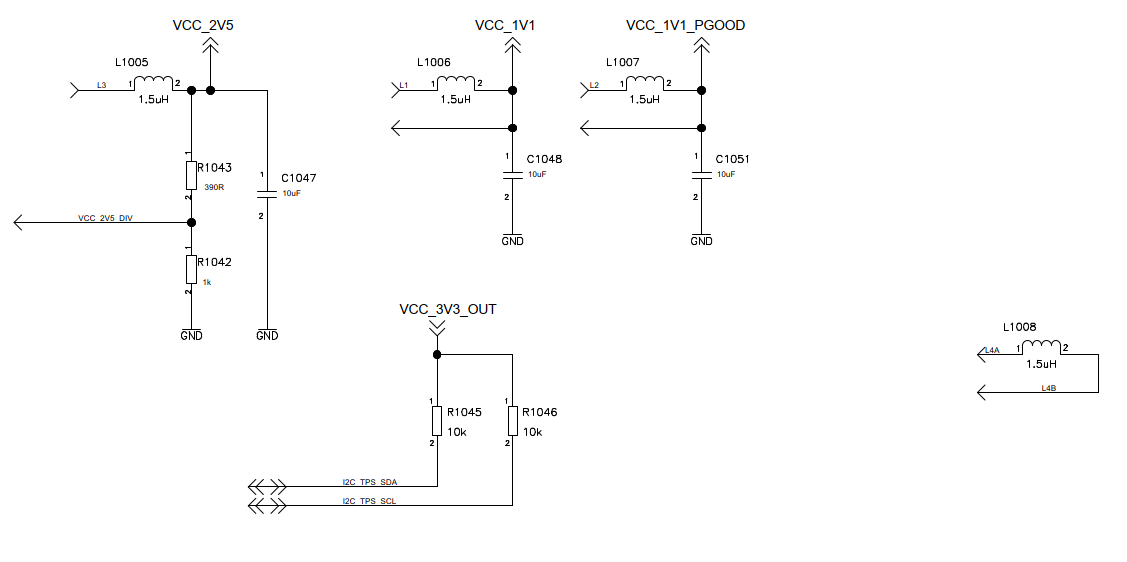

我使用 TPS65218D0为 Cyclone V FPGA 供电。 PGOOD 输出引脚连接到 FPGA 的 nConfig 引脚、以便在电源超出范围时触发 FPGA 的重新配置。 TPS65218不使用 I2C 进行重新编程、所有设置均默认为1、这意味着也是 strict=1。

遗憾的是、当尝试在 FPGA 上配置"更大"的映像时、如果 FPGA 使用适当的逻辑和 I/O、则会发生400ms 的重新配置周期。 其原因是、每次新配置尝试启动时、PGOOD 都会在 amout 1us 的持续时间内变为低电平。

在下面的屏幕截图中、黄色表示 PGOOD 信号直流耦合。 红色信号是 DCDC1的输出、交流耦合、没有带宽限制。

通过测量、我无法检测任何电压变化、从而触发任一电源轨上的 PGOOD 信号。 DCDC1至 DCDC3具有高达20mV 的噪声、DCDC4具有高达40mV 的电压、因此在3.3V 电压下也不会出现问题。

还有什么让我感到困惑的地方、PGOOD 在仅1us 的时间内处于低电平是怎么可能的? 监控的抗尖峰脉冲是否应防止这种情况发生?

当开始重新配置较小的映像时、或使用 FPGA 的 DEV_CLRN 引脚而不是 nConfig 时、系统正常工作。