你(们)好

阅读数据表可知:

Page1:所有电源轨上的 UVLO 保护。

第6页:5V LDO 和 VNEG 的预期输出。

第7页:12V 电源轨的 UVLO 参数。

第13页:图中显示了一个 ULVO 块、该块列出了它监控+5V、VDD 和 VNEG。

第14页和第15页:列出 UVLO 事件会将 FAULT 拖至低电平。

但是、我似乎无法找到可能导致 UVLO 事件的 VNEG 和5V 上的电压电平。 在哪里可以找到它们?

此致

Martin

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你(们)好

阅读数据表可知:

Page1:所有电源轨上的 UVLO 保护。

第6页:5V LDO 和 VNEG 的预期输出。

第7页:12V 电源轨的 UVLO 参数。

第13页:图中显示了一个 ULVO 块、该块列出了它监控+5V、VDD 和 VNEG。

第14页和第15页:列出 UVLO 事件会将 FAULT 拖至低电平。

但是、我似乎无法找到可能导致 UVLO 事件的 VNEG 和5V 上的电压电平。 在哪里可以找到它们?

此致

Martin

你(们)好

相关信息来自 BRC2518T220K。 在我前面的板上、它是 H 桥的 BR (右下角)桥臂、因此它是低侧。 但我也在高侧看到过它。

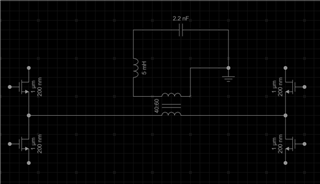

拓扑:H 桥连接到匝数为40:60的变压器。 输出端连接到有损耗的串行 LC 振荡器(电容有意有损耗)、其中一 个变压器输出端连接 到保护接地端。 这是一个极其简化的原理图。

然后将系统驱动为 PSFB、以启动一个非常低的占空比

到底是不是这样破坏降压/升压呢?

此致

Martin

您好 Martin、

Kyle 目前不在办公室、但我一直关注 Kyle 的这条线程、可以为您提供一些建议。

首先、请在器件开启但不进行开关时发送 VDD 和 VNEG 引脚的示波器截图、这有助于进一步缩小问题范围。 在您获取并发送这些测量值后、假设没有明显的解决方案、我建议您更换 LMG3411器件并重新测试。 要重新测试、请在 VDD 未切换的情况下为器件加电、然后开始切换并查看 VNEG 电压问题是否仍然存在。

此建议过去有效、将排除单个器件问题。

此致、

扎赫

你(们)好

我可以回答其中的一些问题而不进行测试、正如我在之前的电路板上已经完成的那样。

我之前的帖子中的示波器图片是 在 LMG3411打开但未切换的情况下显示的。 由于/FAULT 处于激活状态、因此我不会向 LMG3411发送脉冲。

我需要进行一些修改、以便在/fault 被置位时允许系统切换。 我可以在星期一进行这些操作。

这是我在板上遇到此问题的第三个板。 不过、最后两次、我们没有时间深入研究它、只是 直接替换了 LMG3411。 之后、电路板再次工作。 很明显 、LMG3411一直在工作、几个小时后、开关出现了此问题。 我在 H 桥的高侧和低侧 LMG3411上都看到了它。 我意识 到问题可能是我要应用的用例、但器件似乎只有 VNEG 超出规格而中断的方式似乎有点奇怪。

此致

Martin

您好!

首先、我想了解您发送的波形的更多信息、器件似乎根据开关节点电压进行开关。 也许我对这个问题的解释不正确、如果可以的话、请详细说明。

根据您的其他信息、以及这似乎不是一个非正统的用例、我相信部分电路以接近峰值的值运行、或者一些瞬态事件导致器件在几个小时后发生故障。

如果 VDD 引脚遇到瞬态事件、则很容易损坏 VNEG 引脚、因为 VDD 电压为用于生成 VNEG 的电路供电。 您能否分享有关"12V_HVDC_TL"引脚的来源的更多信息?

谢谢、

扎赫

你(们)好、扎赫

设备未在先前帖子中的图像范围图像中切换。 我刚刚从稳压工作台电源施加了12VDC、它报告说它的电源电流为50mA。 我认为您对示波器图像的解释不正确。 当 IN 信号保持低电平时、它们显示 VNEG 和开关节点。

如果您有时间对此进行进一步调查、我可以共享设计文件。

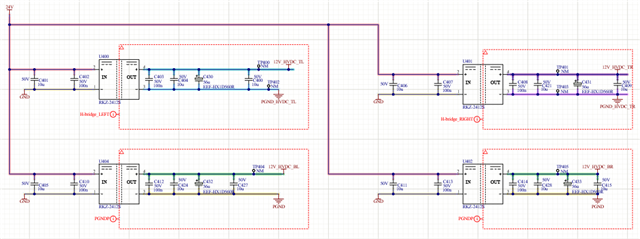

12V_HVDC_TL 来自隔离式电源、如下所示。 H 桥的每个桥臂各一个

HVDC 至 PGND 轨为360VDC、因此没有接近峰值的电压轨。 我自己认为一个瞬态事件是问题的罪魁祸首、但器件应该以这种方式中断仍然很奇怪。 我目前正在硬开关电流、我正在研究是否可以更改为软开关。

// Martin

我现在看到,感谢作出澄清。 这个问题似乎并不明确、如果您想共享您的设计文件、我可以查看原理图或布局中是否有任何东西会被卡住。 可能存在一些布局问题、导致 VDD 引脚产生噪声、我将查看该问题、但也希望管理预期结果。

请随时联系我的电子邮件(z-soviero@ti.com)并共享设计文件。

谢谢、

扎赫