主题中讨论的其他器件: LM5066、 CSD19536KTT

您好!

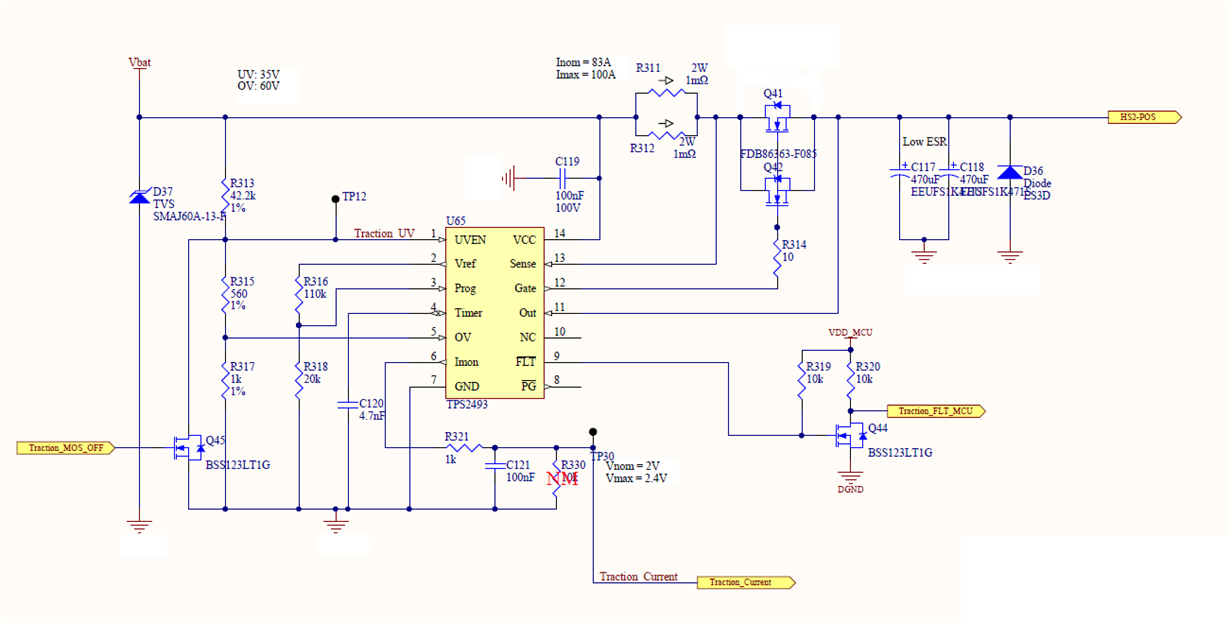

我会使用 TPS2493来保护具有100A 电流限制和50V 标称电压的电机。 我设置电阻器网络以获得以下值:

UV = 35V (UVEN 引脚1上的分区 为0.7V)

OV= 60V (OV 引脚5-上的分区为0.46V)

VPROG= 0.615V (在引脚3上)、将功率限制在大约600W

我使用了两个 MOS " FDB86363-F085"

感应电阻为0.5m Ω

所有器件都按照数据表中的参考原理图进行连接、但我会遇到无法理解的行为:

-当我使用160Ohm 的电阻负载时、一切正常、我发现 UV 和 OV 阈值与预期完全一样、因此电流仅在35 <Vcc<60 Volts. 时流入负载

-当我使用1欧姆的电阻负载时、即使 Vcc=20V、MOSFET 也会关闭(电流流入负载)。 由于某种原因、栅极似乎已启用、应该位于 TPS2493内部。

我们非常感谢您的任何支持。

非常感谢

此致