大家好、团队、

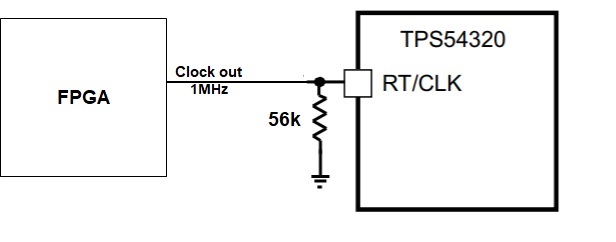

我正在考虑如何使用 TPS54320 1MHz 外部时钟来决定开关频率。 我设计的方框图如下。

在上电期间 、我将 FPGA IO 的 IO 设置为高阻态、并通过 RT (56k)设置的内部时钟将 TPS54320上电。 但在高阻态期间 FPGA 的泄漏电流过大、并且 RT/CLK 引脚中的电流从所需的电流值发生变化、 开关频率增加。 因此、我正在考虑如何配置 RT/CLK 引脚。

您是否建议我避免增加 RT/CLK 引脚和 FPGA 输出之间的开关频率和最佳配置?

非常感谢您的支持。

此致、

Akihisa Tamazaki