您好!

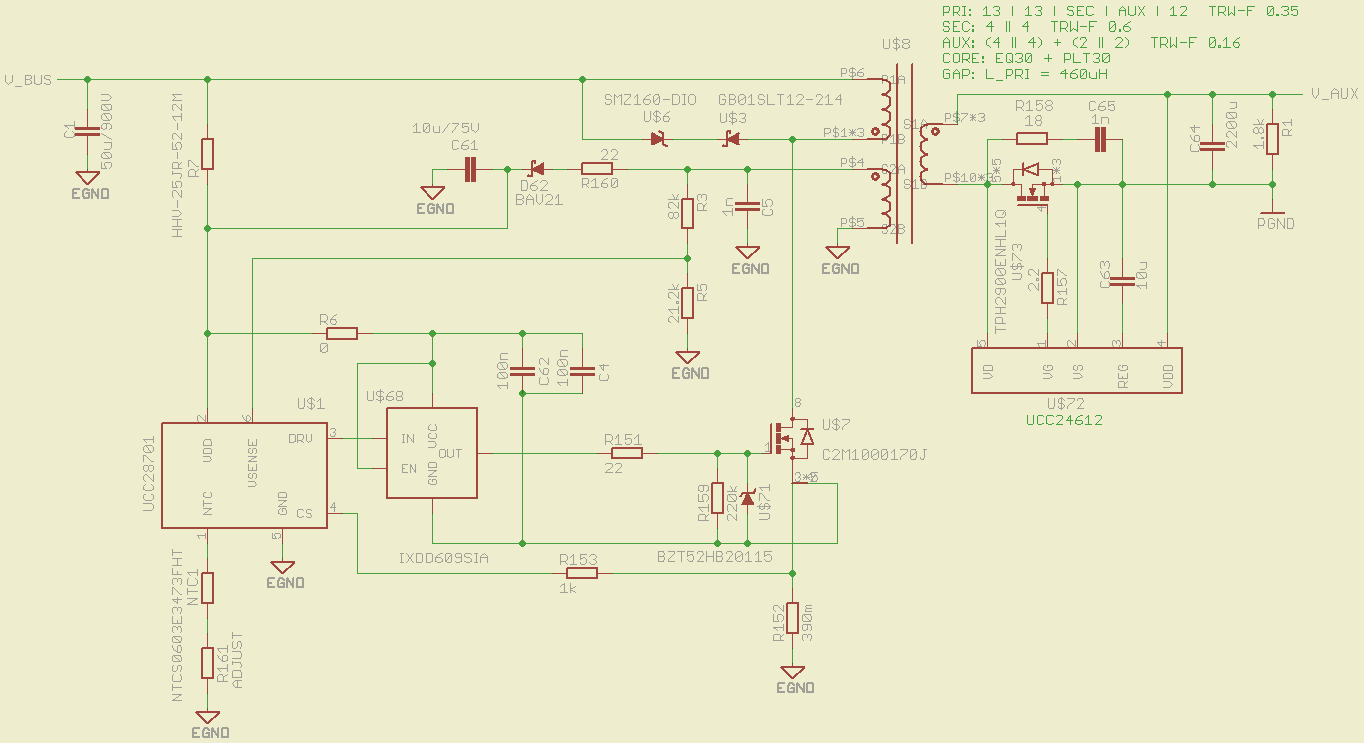

我正在基于 UCC28701对14V/4A 反激式器件进行原型设计。 它工作正常、但我可以观察到以下神秘行为:

在输入电压为320V 的空载条件下、转换器进入多次重启序列。 它最终会终止、输出端存在15.5V 电压。 如果我将输出端的虚拟负载电阻器减小到比数据表中给出的公式计算出的值小~2倍、那么它将 以可靠的方式开始。

2.如果 I_OUT 小于约3A、则输出电压接近所需的值、并在整个范围内保持稳定。

3.如果负载电阻降低使 I_OUT 超过3A 限制、控制器将再次进入重启序列。

4、如果负载进一步降低、控制器将再次进入稳定区域、并以4.1A 的恒定电流输出~9.5V 电压。

如上所述、CV 和 CC 之间的转换不平稳、控制器拒绝运行的转换区域非常宽。 这种行为的原因可能是什么?

如果您还可以在(1)中解释断续模式、也将受到高度赞赏。

如果需要更多详细信息、只需提问即可。 以下是一些:

L_pri = 405uH、N_pri / N_sec = 9.5 (38pri:4sec:6aux)、

R_CS=350m Ω

R_LC=1k

R_s1 (顶部)=82k

R_s2 (底部)=20k

V_IN = 180..900V 直流

V_IN_RUN=117V 直流

V_dd =~20V

此致、Piotr