在我们内部设计的栅极驱动板上、FLT 引脚为低电平、但我不知道原因。

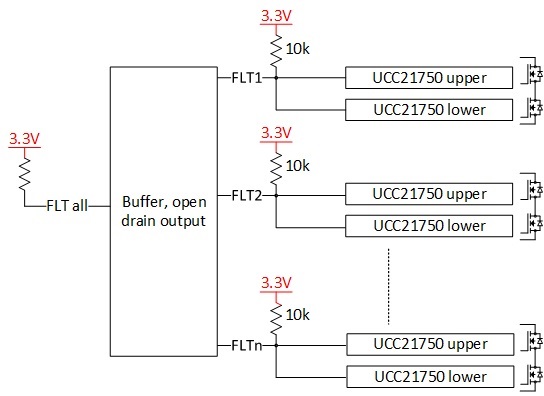

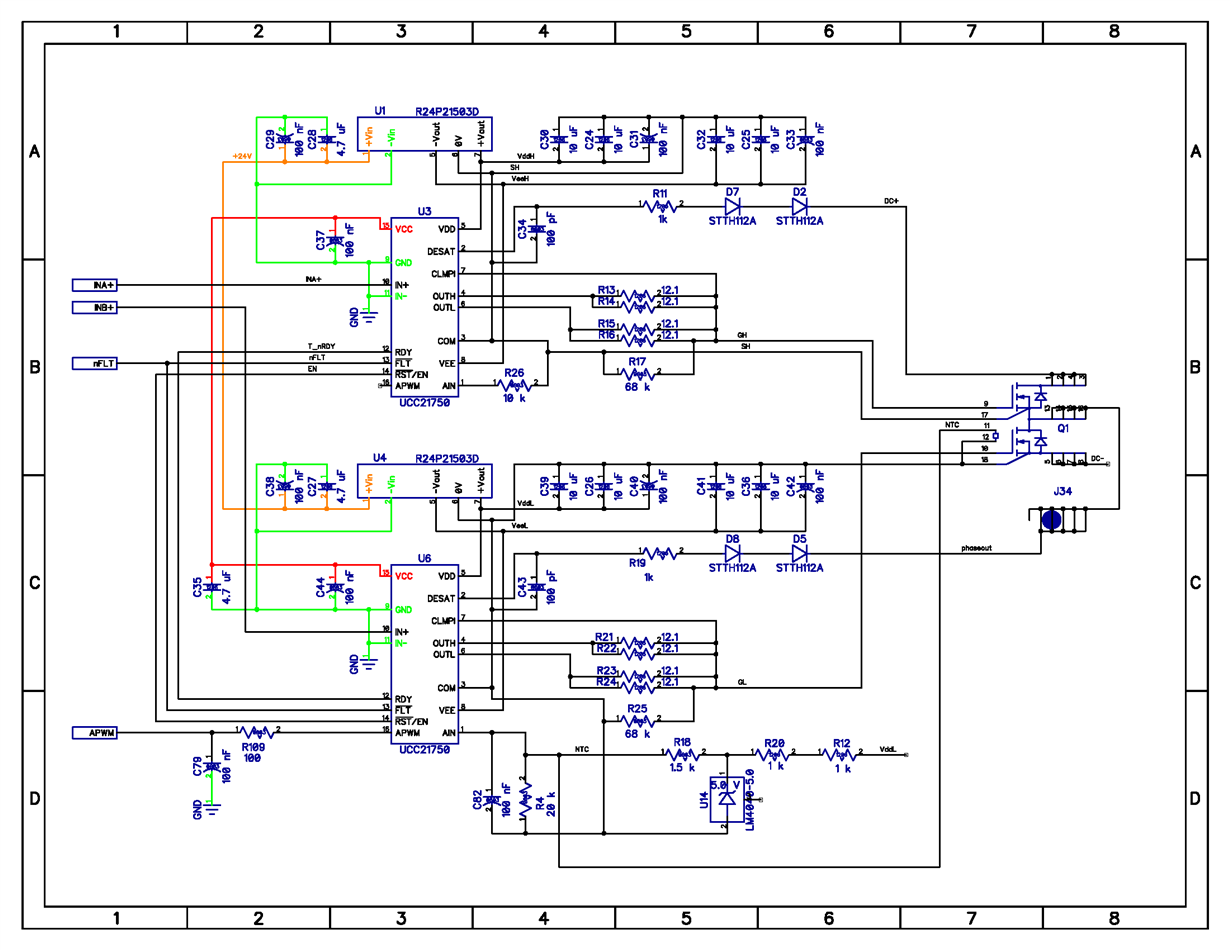

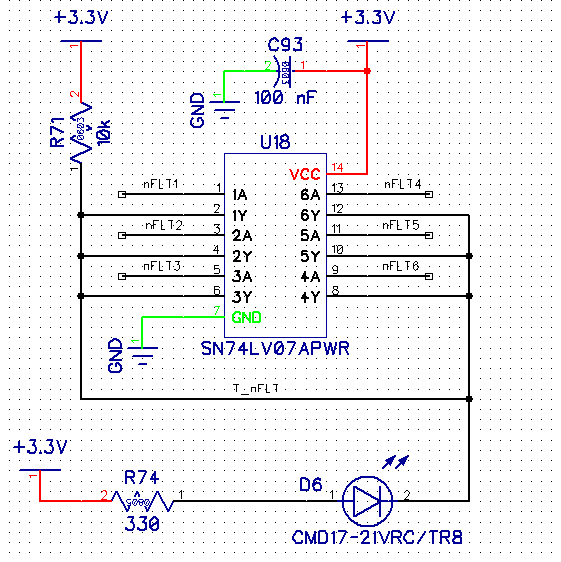

基本配置如下所示。 板上有多个 UCC21750芯片;一对 UCC21750 (用于驱动半桥)将其 FLT 引脚连接在一起并通过10k 电阻器上拉。 然后、这些 FLT1-FLTn 信号被馈送到缓冲器中、其中 FLT 信号与一个 FLT_ALL 信号进行组合。

在电路板上、FLT1至 FLTn 均为低电平、这表示 FLT、但 DESAT 引脚仅为200mV。 其他引脚的读数如下。

| UCC21750UPPER | UCC21750更低 | |

| IN+、IN- | 0V | 0V |

| RDY | 3.3V |

3.3V |

| 弗尔特 | 0V | 0V |

| RST/EN | 3.3V | 3.3V |

| VCC | 3.3V | 3.3V |

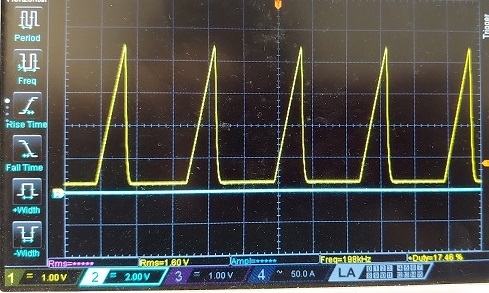

| APWM | 占空比为60%的0-3.3V PWM | 占空比为38%的0.5-2V PWM |

| Vee | -3V | -3V |

| CLMPI、OUTL、OUTH | -3V | -3V |

| VDD | 15.8V | 15.8V |

| DESAT | 200mV | 200mV |

| AIN | 2V | 3V |

APWM 和 AIN 分别为38%和3V 的 UCC21750lower 具有用于 AIN 引脚的外部电路、旨在连接至 MOSFET NTC。 UCC21750UPPER 具有一个用于 AIN 的10k 下拉电阻器。 这就是为什么上限和下限 AIN/APWM 是不同的。

什么可能导致 FLT 被拉低?