主题中讨论的其他器件: LMR14006、 UCC27282

大家好、团队成员

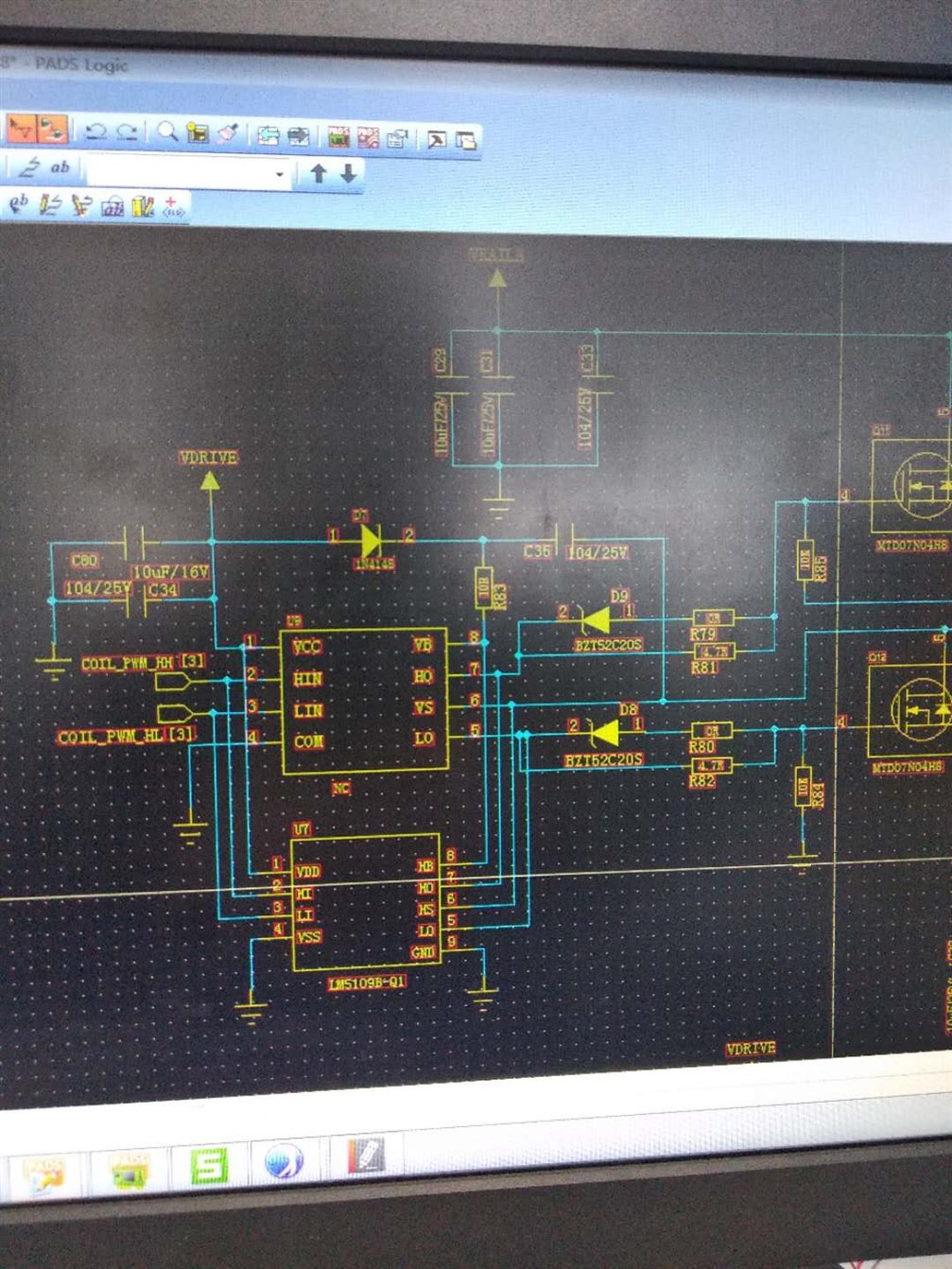

我的汽车客户在其汽车无线充电器产品中使用 LM5109B-Q1。 它们使用 LMR14006将 BATT 12V 转换为8.3V、并将其转换为 LM5109B-Q1的 VDD 引脚。

客户对系统的 BATT 12V 输入执行电源压降测试。 当测试执行时、BATT 12V 将以不同的频率下降至0V。 测试将持续约1分钟。 客户要求系统在测试完成后应正常工作、但 LM5109B-Q1无法正常工作。

测试期间存在 HI 和 LI 信号输入。 经过功率压降测试后、LM5109B-Q1 HO 和 LO 输出信号占空比分别小于 HI 和 LI 引脚上的输入信号。 只有关闭 LM5109B-Q1电源并为其加电、才能使其正常工作。

如果客户将 LM5109B-Q1更换为 IR2301、则测试通过。

是否有人就此问题提出建议?

以下是客户动态信息:

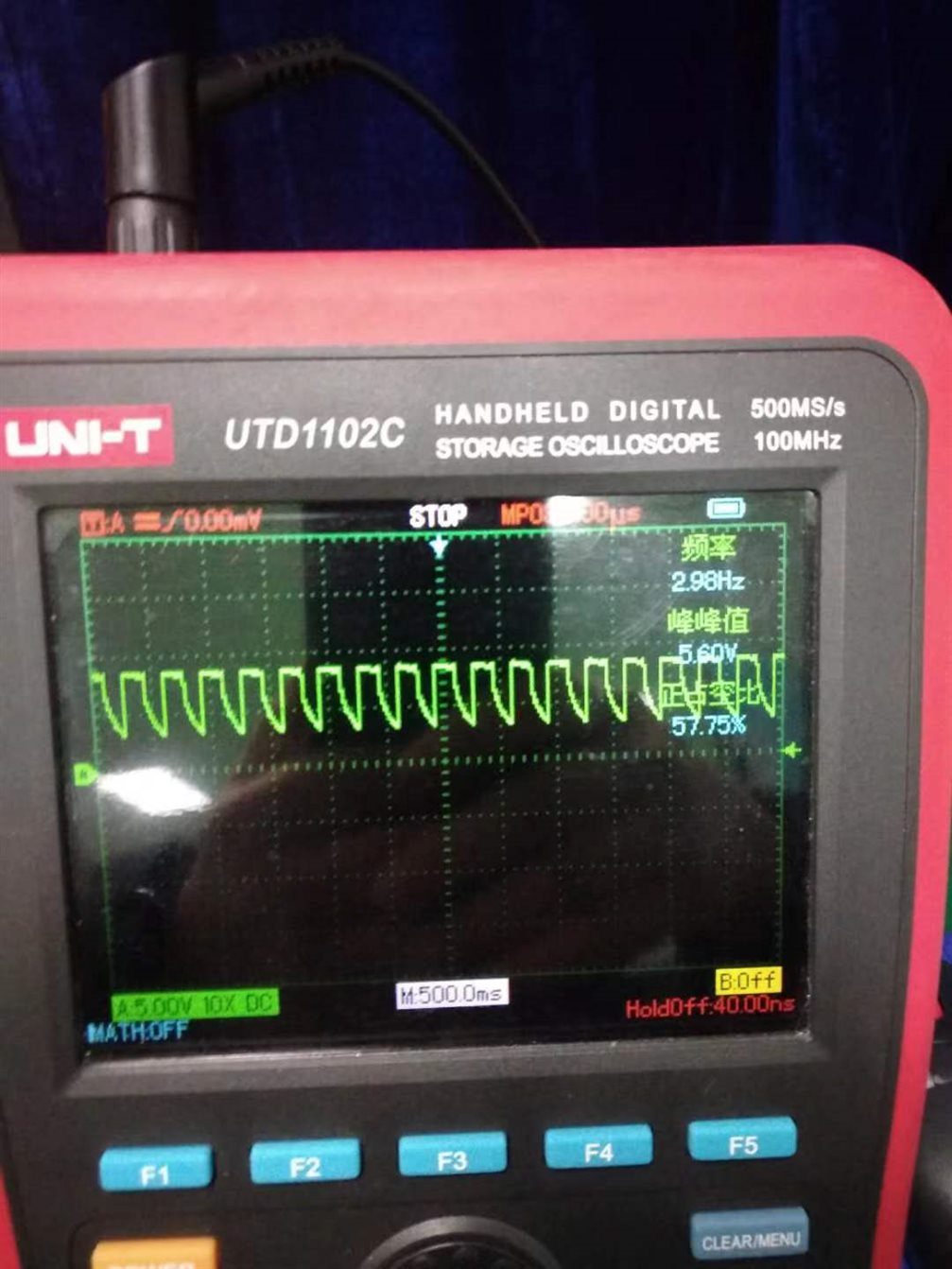

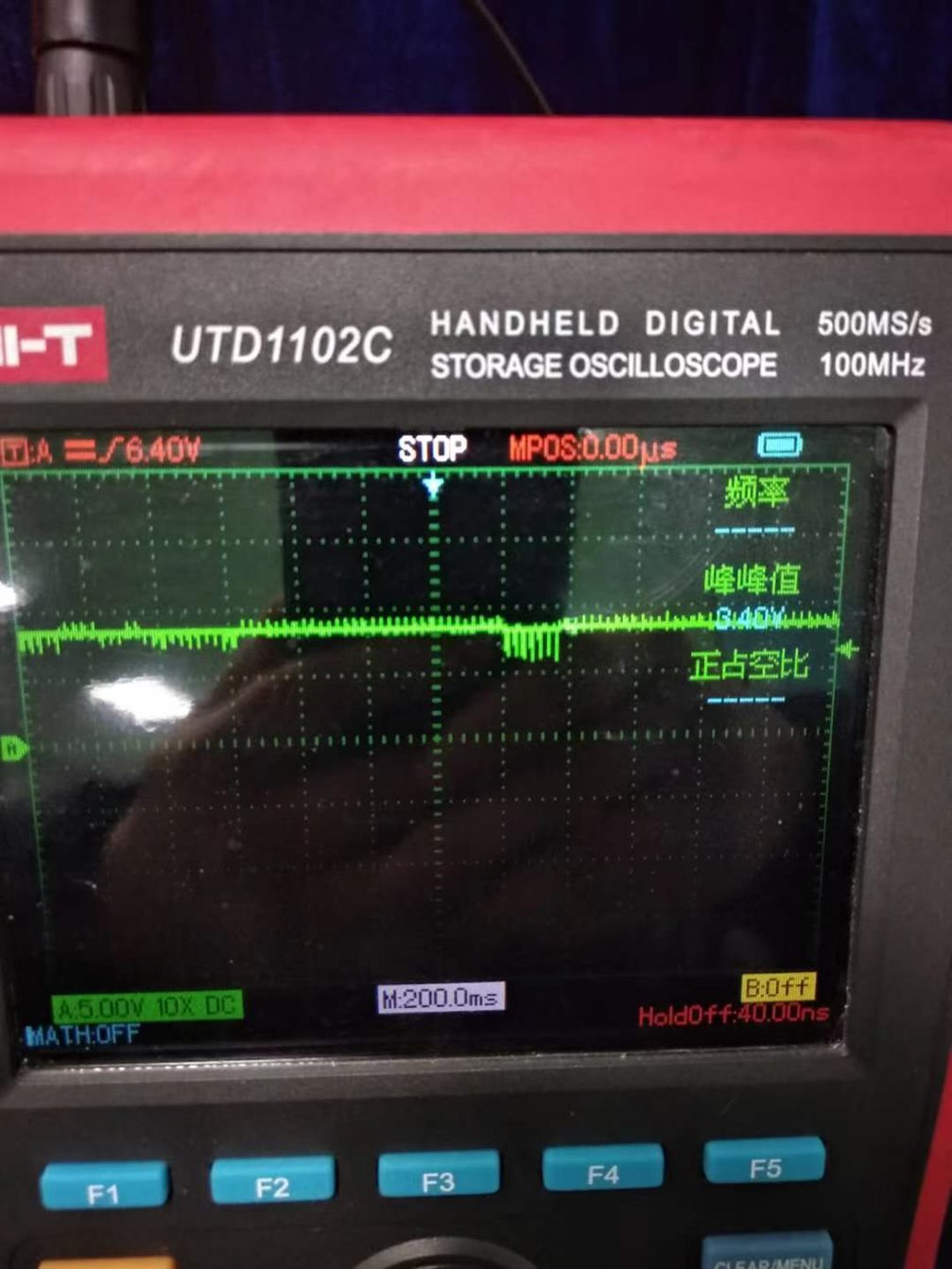

这是 BATT 12V 的 hte 波形。

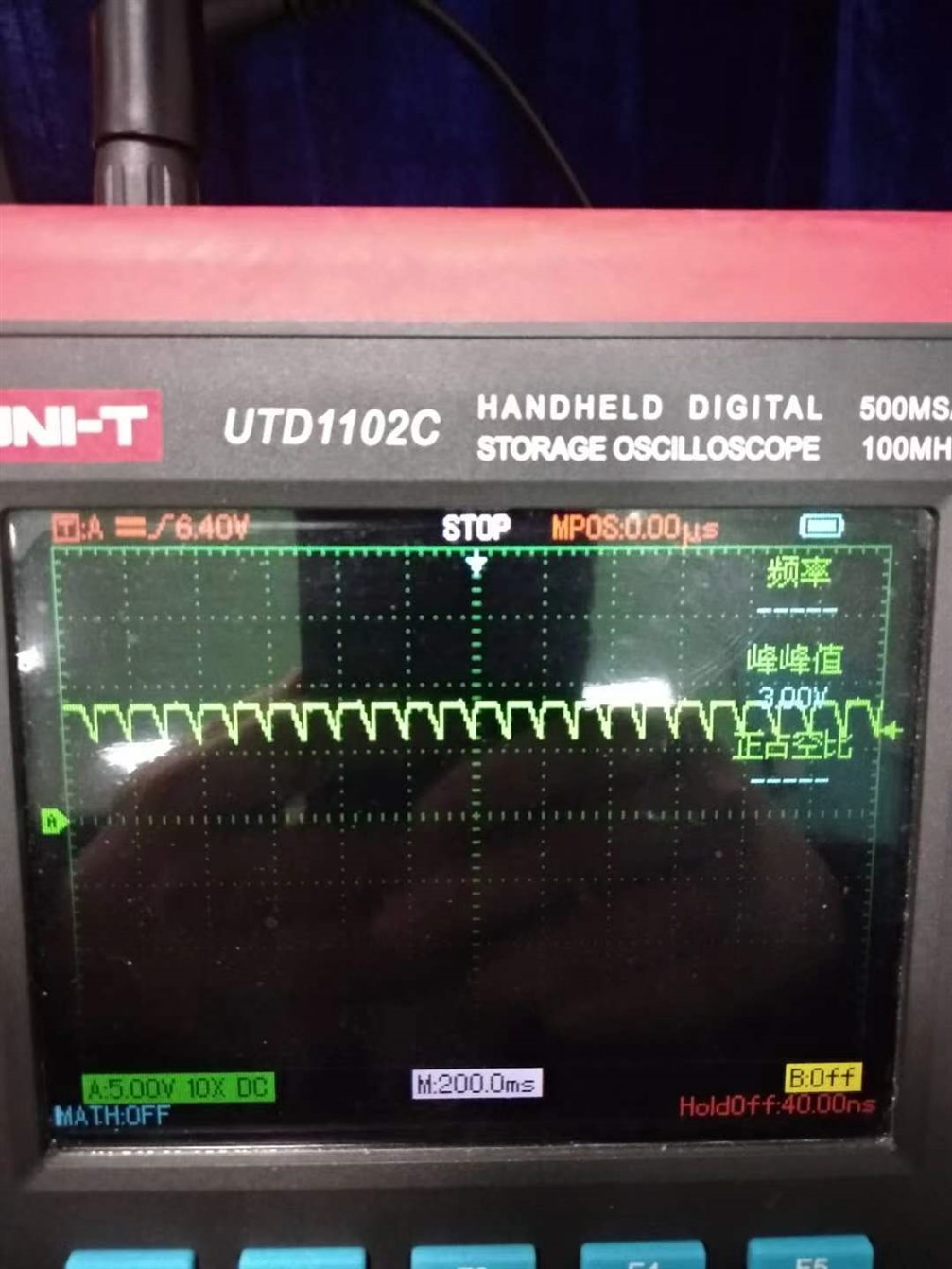

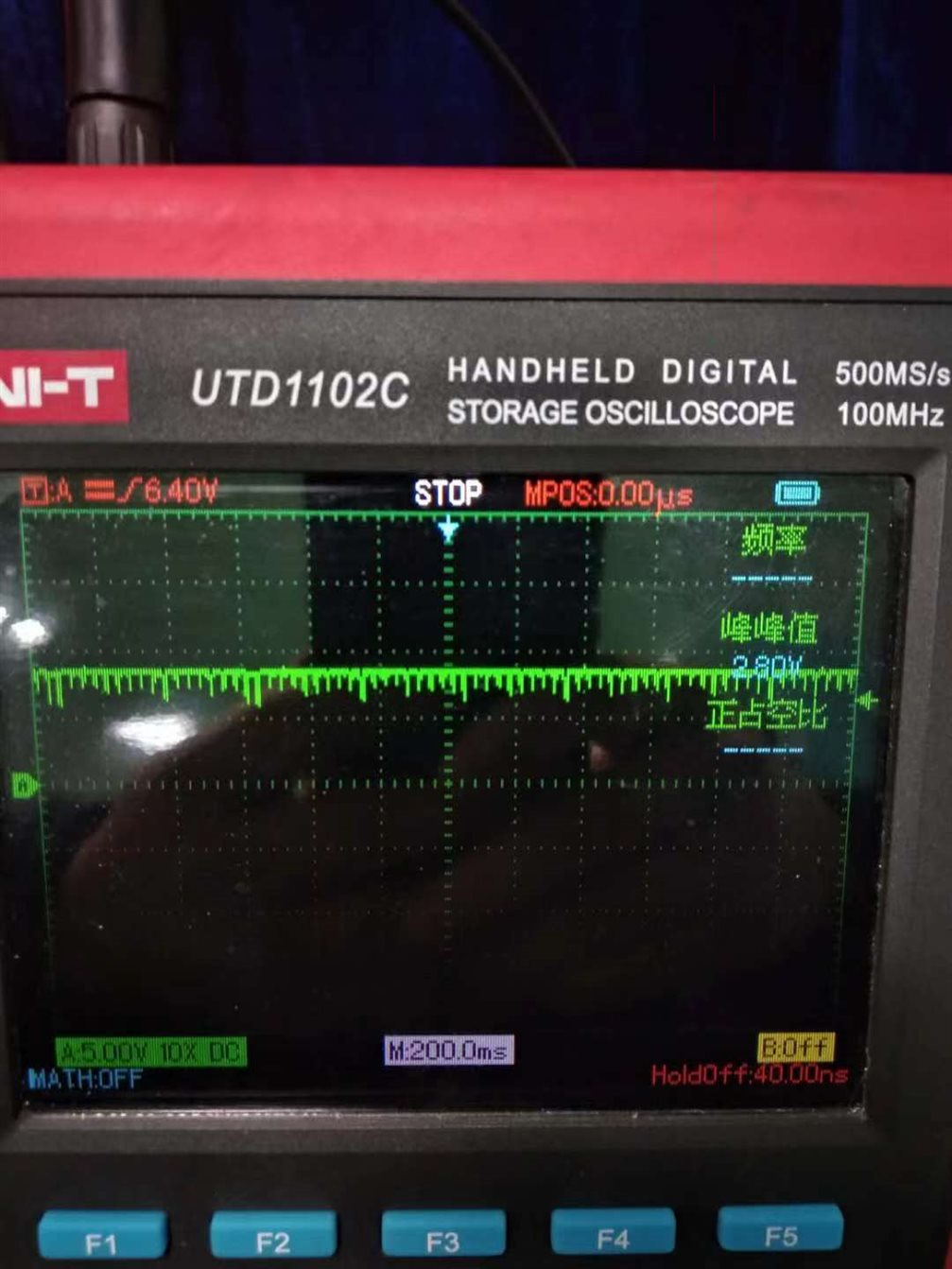

这是测试期间 VDD 引脚上的波形。 VDD 电压将降至3V 以下。

谢谢

Kevin