Other Parts Discussed in Thread: TPS562201, TPS562208, TPS54202

主题中讨论的其他器件: TPS562208、 TPS54202

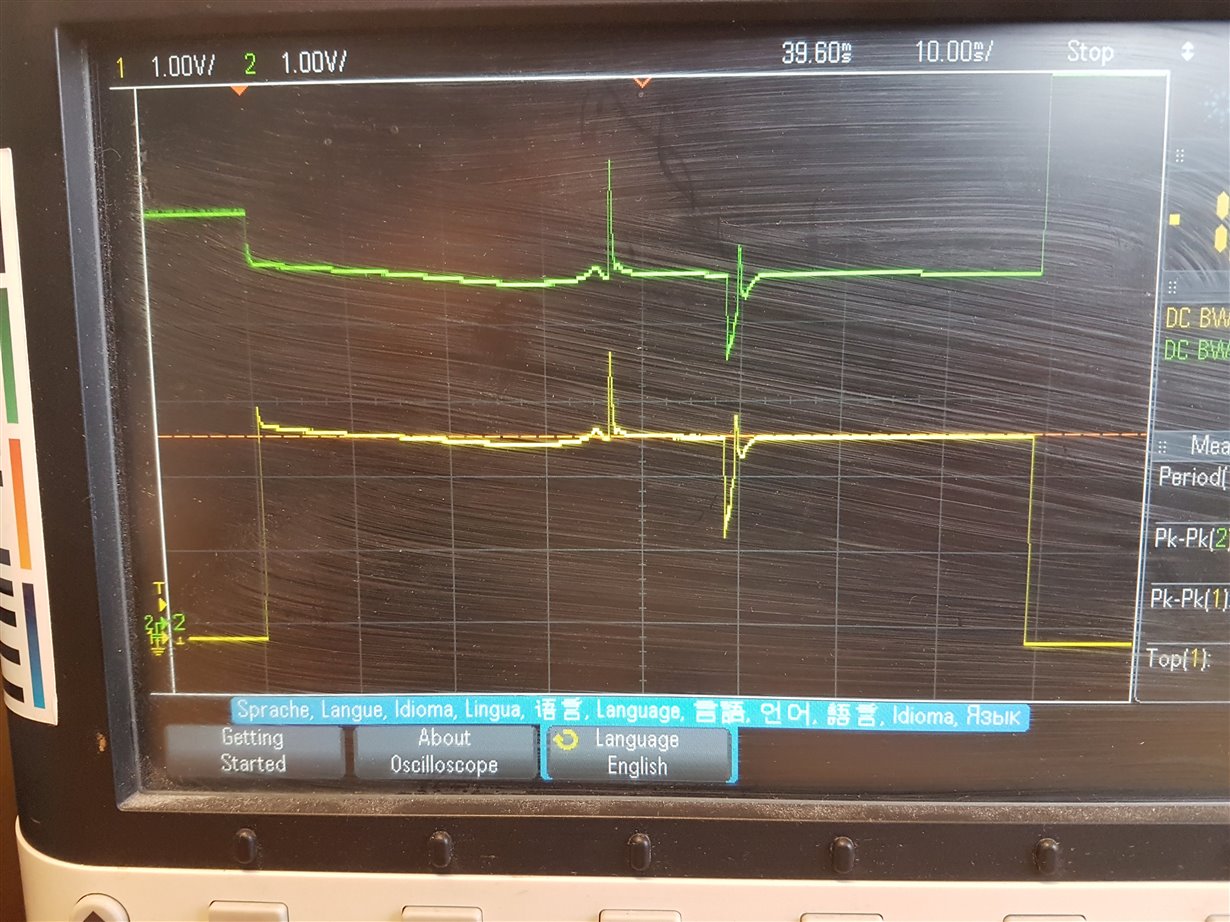

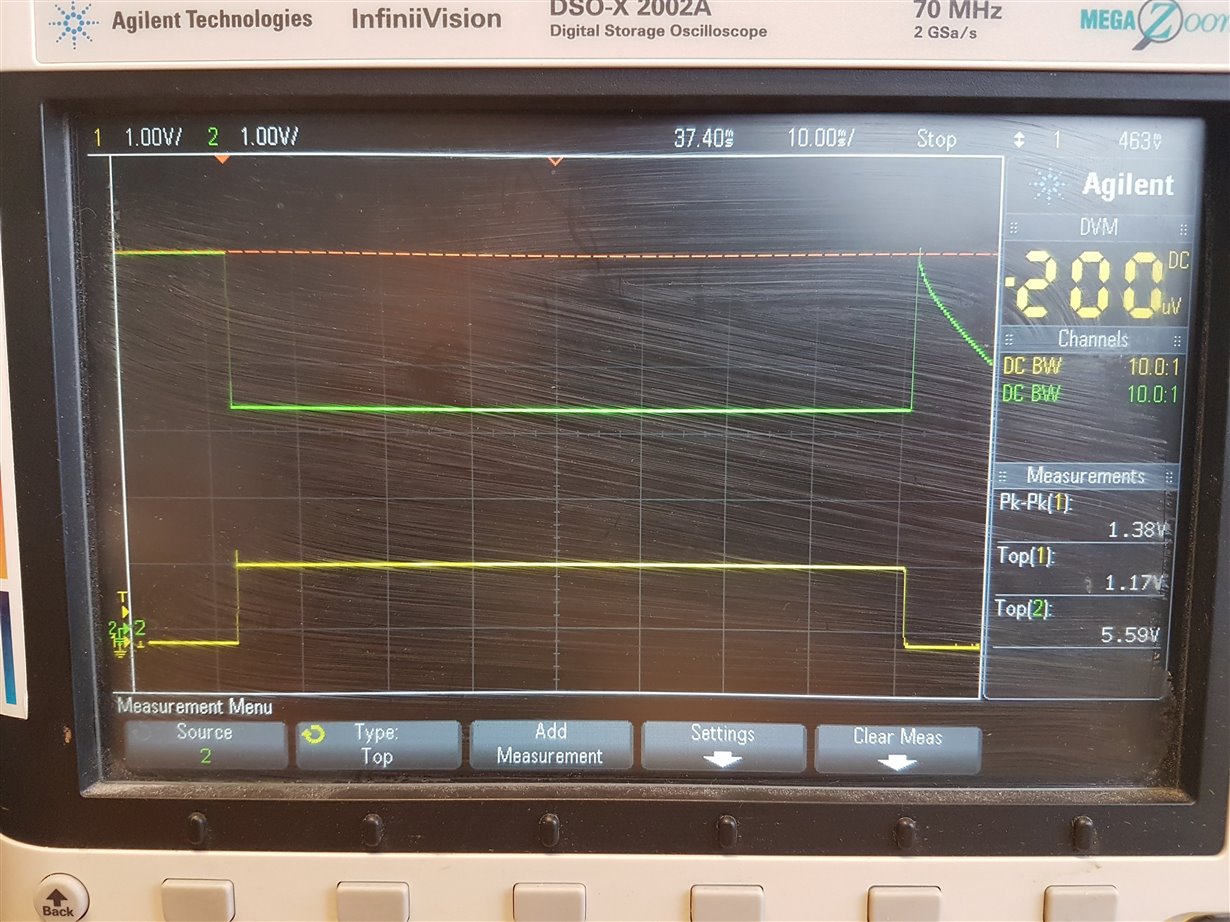

当 TPS562201的输出短接时、IC 不会保护自身、而是会熔断。

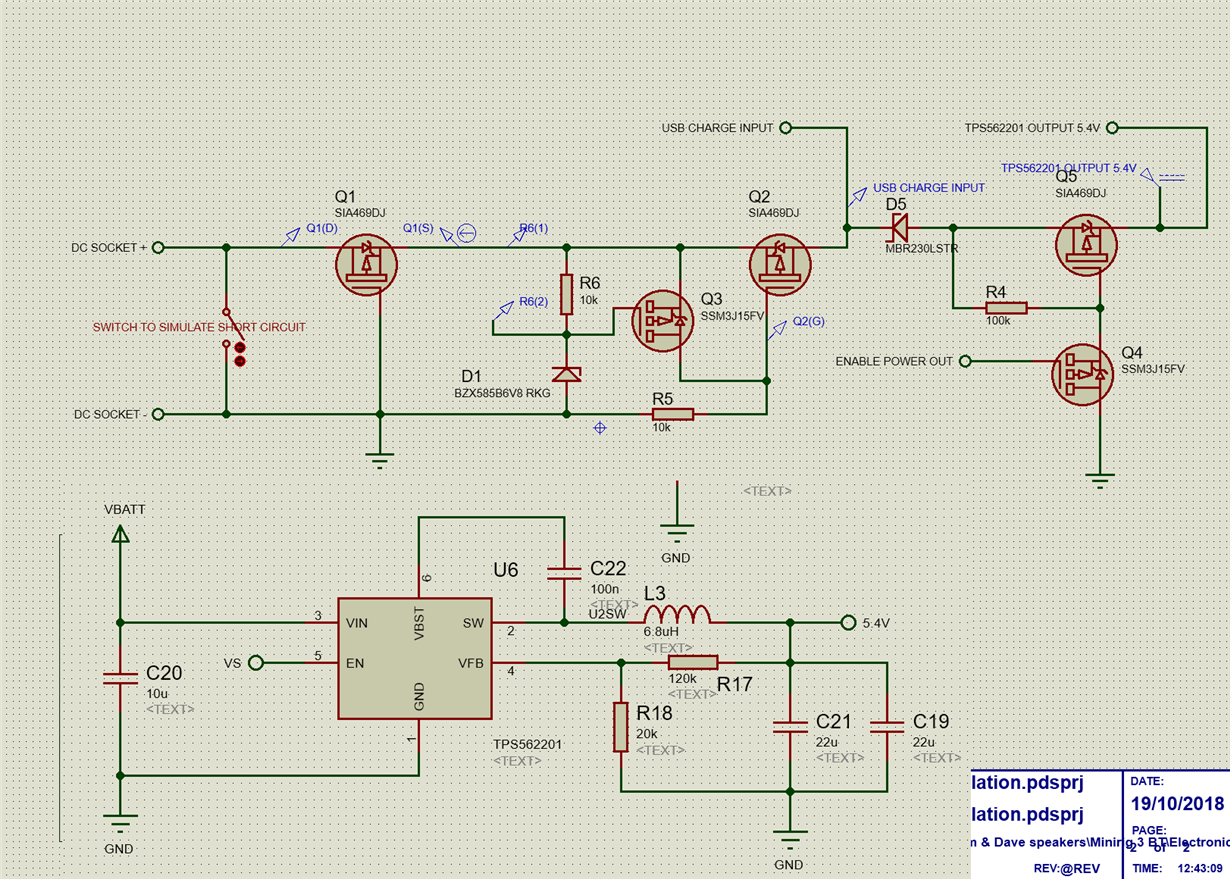

TPS562201用于生成5.4V 电源轨、用作"USB 电源输出"。 尽管此输出具有电流保护功能、但激活通常需要10-50mS 的时间、此时 IC 会爆炸。

我的问题是:

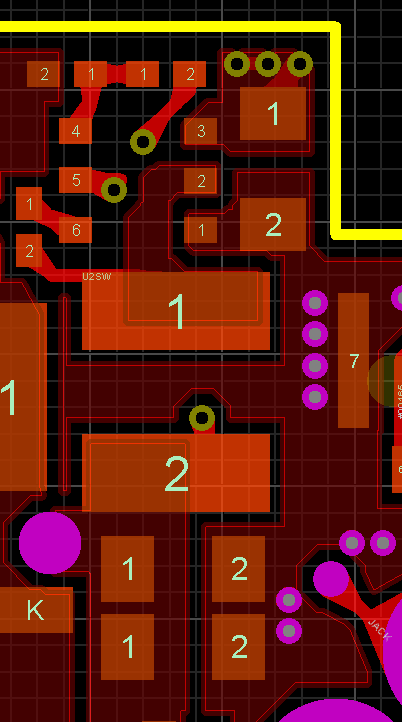

1) 1)该 IC 是否能够在不损坏自身的情况下处理输出短路?

2) 2) 2)您能否建议焊盘/引脚兼容 IC CAN?