请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS53659 尊敬的专家:

我们希望验证 SVID 的质量、我们需要知道 VR 芯片端的"电压定义"。

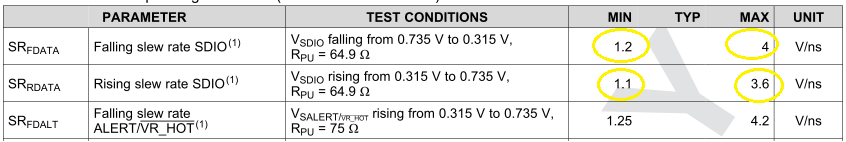

我们是否可以遵循"4.11登录接口引脚"规范、如"下降/上升压摆率 SDIO"?

(但我们的测试结果(0.3~0.7V/ns)低于这些规格.....)

这些4.11规范似乎与英特尔文档544905 "表3-2 "指南相同、但英特尔提供了注释"压摆率仅通过 VR 缓冲电容定义。 压摆率不是一个关键的验证参数、而是被使用

以供 CPU 和 PWM 供应商设计输出缓冲器"。

因此、这些标准似乎不适合我们的板级验证。

请建议我们遵循哪些 SVID 电压标准? 谢谢你。