请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:UCC28C42 您好、TI、

在确定 UCC28C42器件的 CS 至 OUT 延迟特性方面需要您的帮助。

您能告诉我这种情况的测试方法吗?

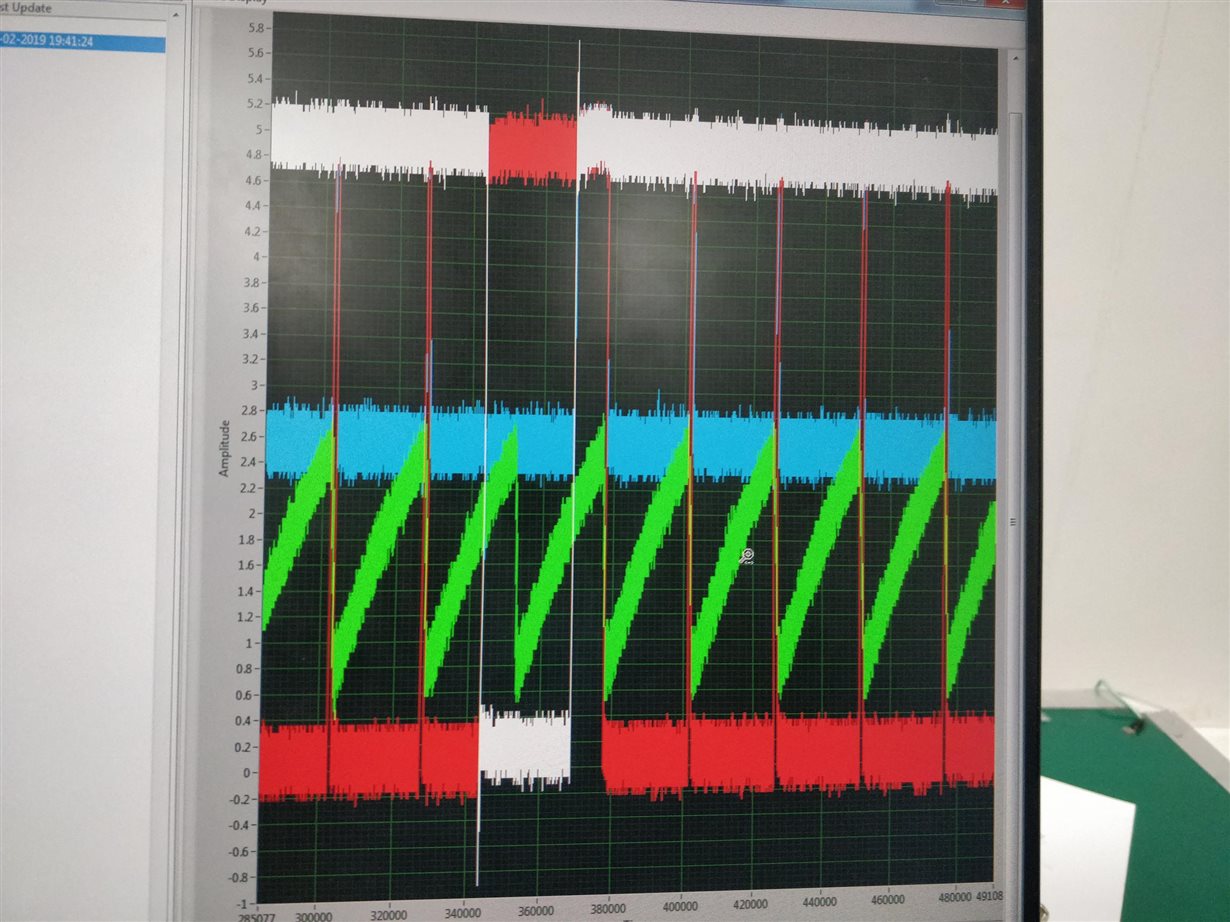

我尝试将 CS 电压从1.1V 更改为0V 并监测 PWM 信号、但由于 RTCT 时钟处于中间状态(绿色波形)、PWM (红色波形)在下一 RTCT 周期上升沿开始前不会改变其状态。 我的 CS 引脚在 RTCT 时钟周期之间从1.1V 切换至0V。 由于 RTCT 时钟是器件的输出、因此我无法使 CS 输入与 RTCT 时钟同步。

此致、