您好!

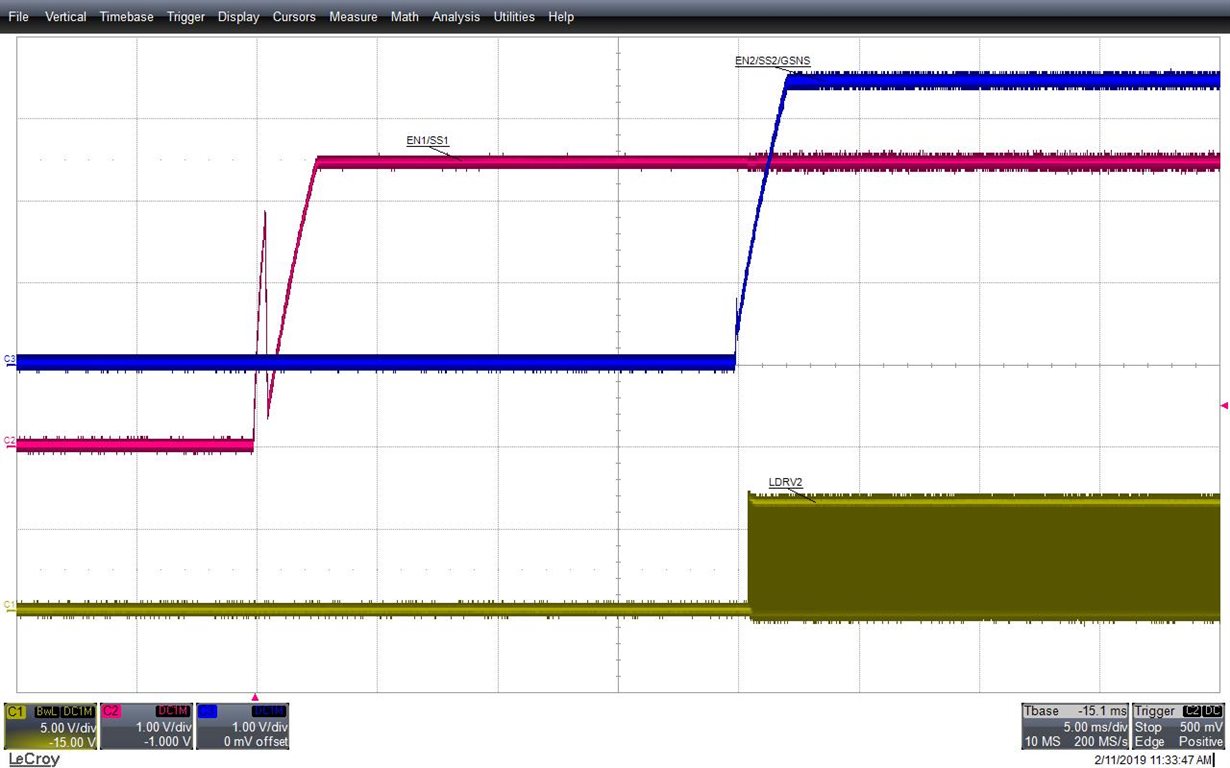

我在 TPS40322上单独使用 EN1/SS1和 EN2/SS2来对 FPGA 的上电进行定序。 我在每个使能之间设置20ms 的延迟。

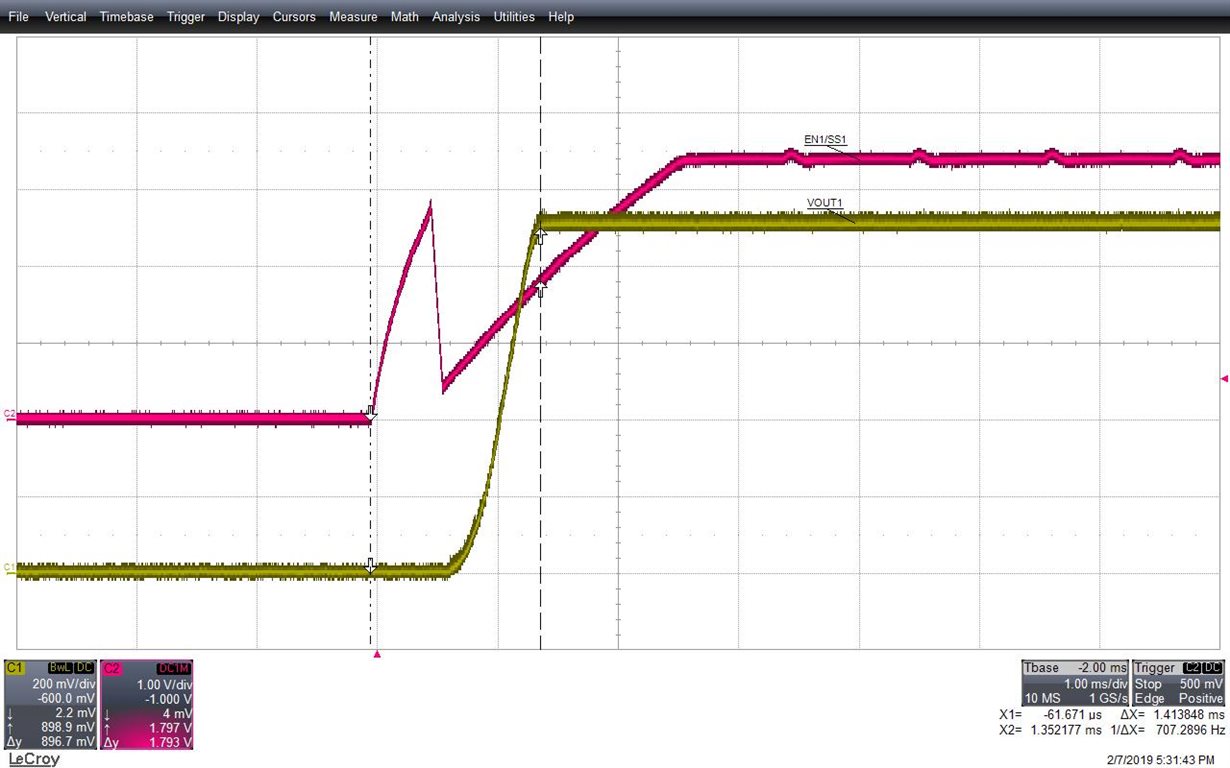

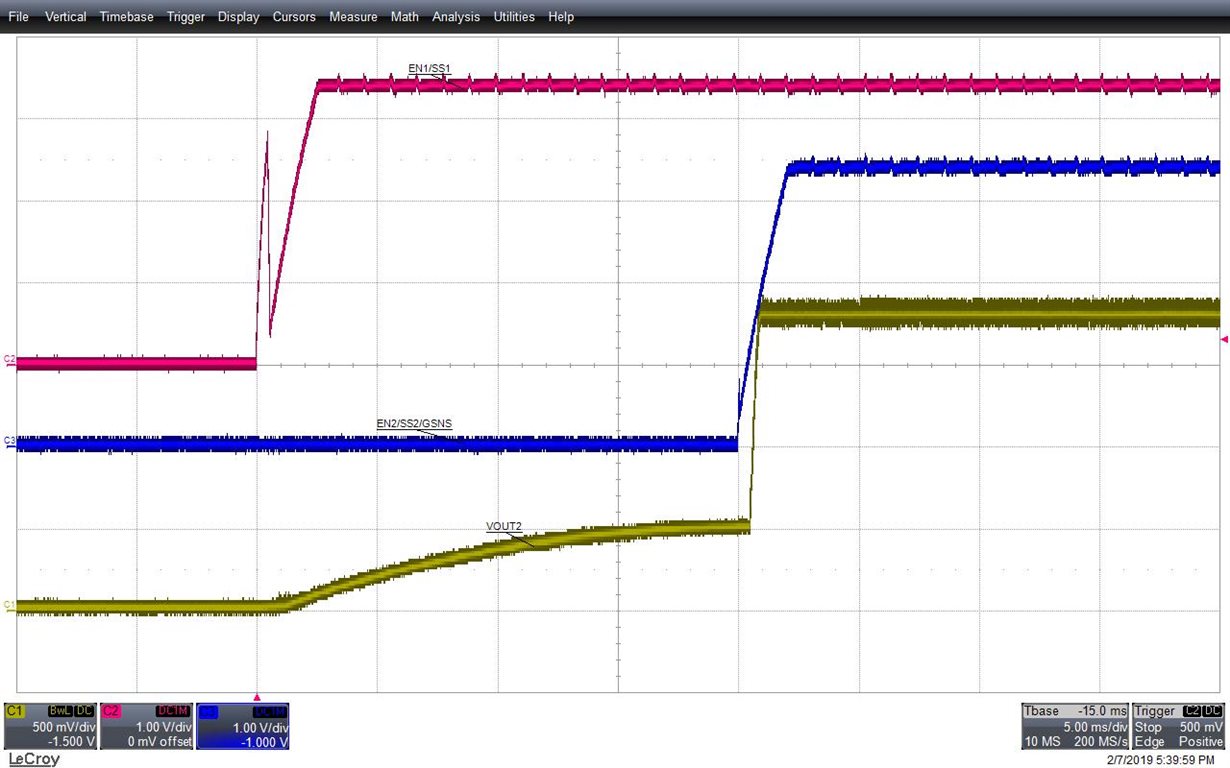

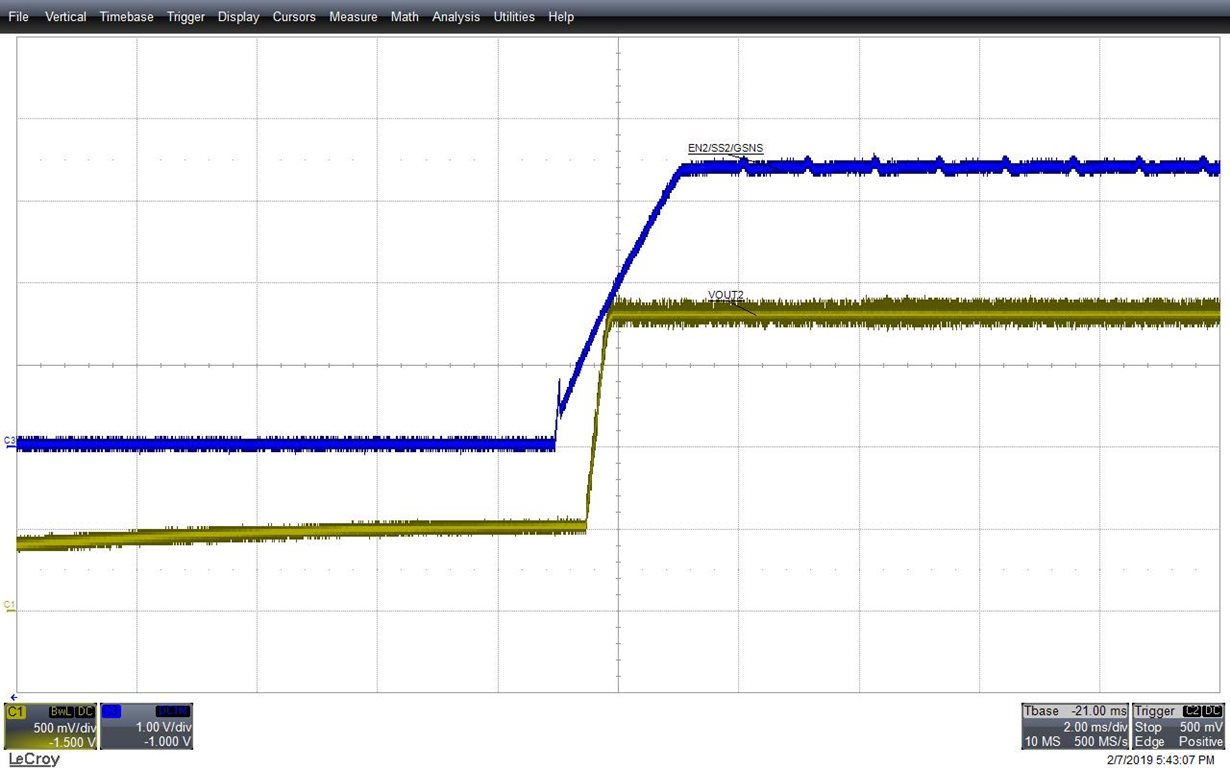

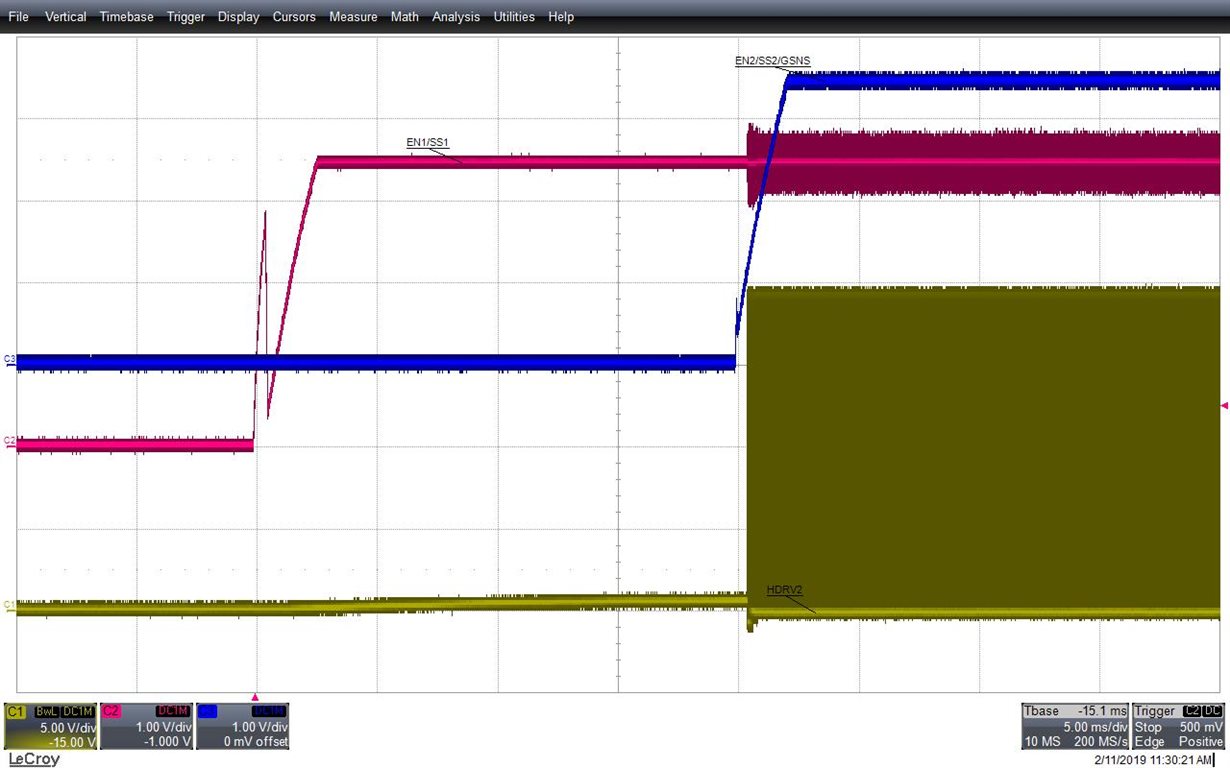

当我启用控制器的 CH1时、VOUT1 (0.9V)正常启动、但同时 VOUT2电压缓慢上升约0.5V、并在我启用 CH2时上升至1.8V。

我的问题是:

Q1_这种行为在 CH2上是否正常、或者在我的设计中引入此残余电压是否有错误? 在启用 CH2之前、我不希望它有电压(FPGA 要求)。

Q2_为什么 EN1/SS1和 EN2/SS2未达到仿真中观察到的 BP6? (它似乎被钳制在一半 BP6上)

查找随附的原理图和3个波形捕捉:

EN1&VOUT1

EN1&EN2&VOUT2

EN2&VOUT2

此致、