请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TPS65094 尊敬的先生:

我叫 Alec Chen。 FAE 表 WT。 我们的客户在其设计中使用了 TPS65094。 当他们测量加电序列时、根据 Intel 上电序列控制规范( 请参阅以下内容、S3/S4信号同时加电)、他们会发现 加电序列与 TPS65094规范不同。

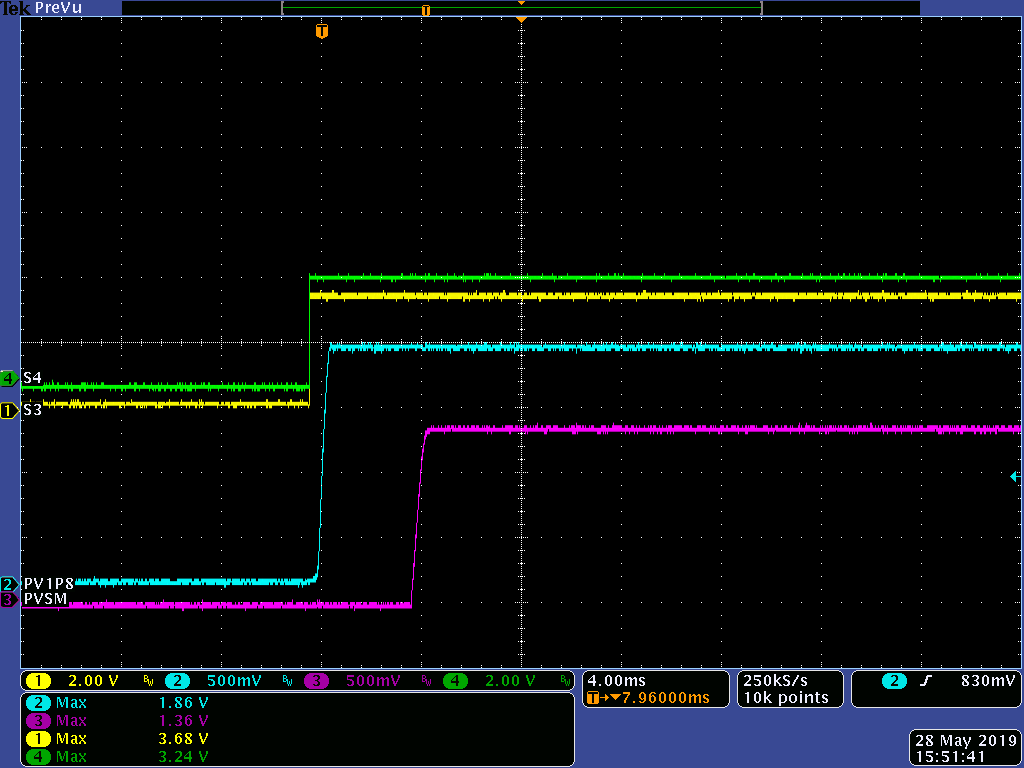

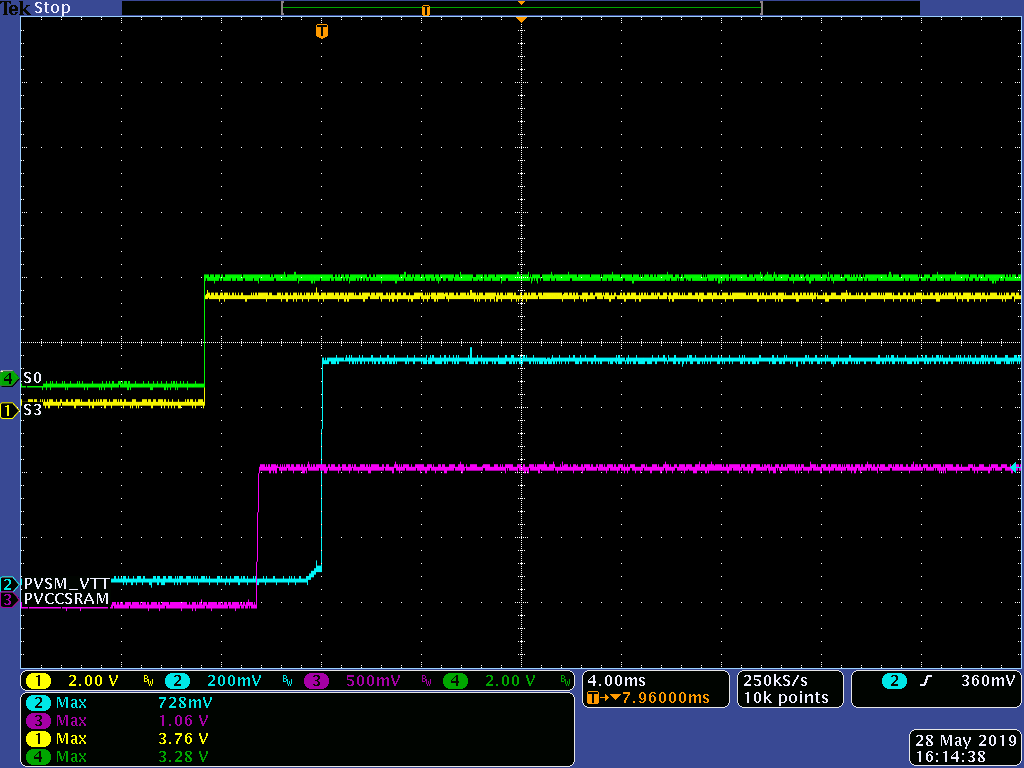

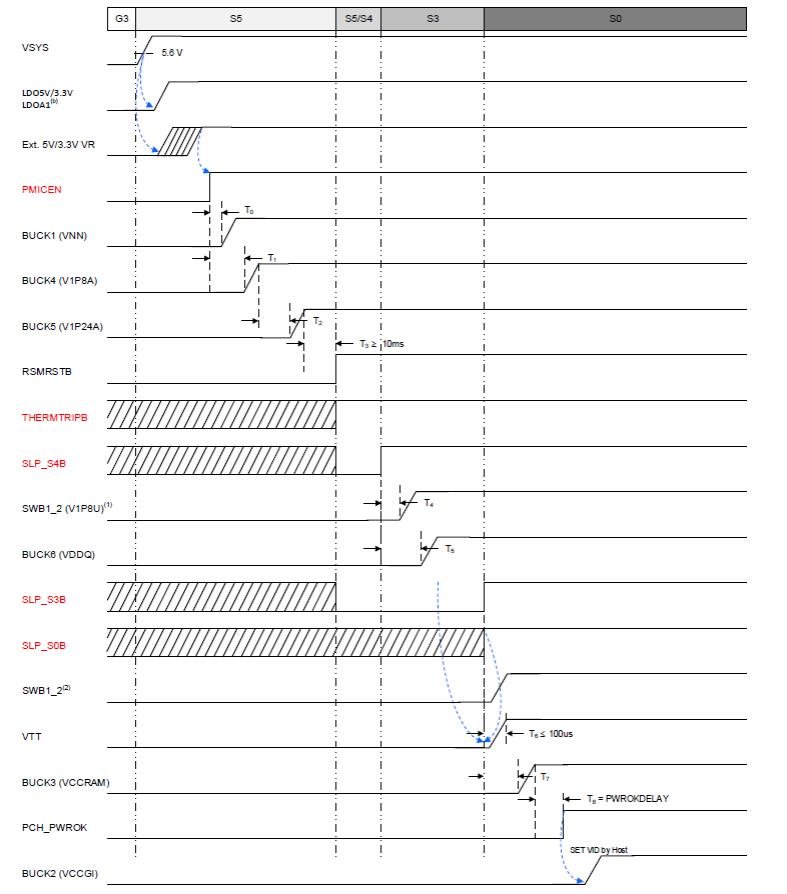

下面是上电顺序、用于测量在 VDDQ 之前哪个 PV1P8上电、PVSM 上电晚于 P12V、PVCC5、PVCC3和 PVCCRAM 上电早于 VTT、VCCGI。 它们与 TPS65094中的加电顺序不匹配

我们发现测量的波形与有关 S3/S4序列的 TPS65094规格之间的差异。 Intel 规范显示 S3/S4信号为高电平、同时 TPS65094规范显示 S3和 S4不是高电平(请参阅规范中的加电序列)、这就是这两者之间存在差异的原因。

我们已就此向 RD 进行了说明、他们仍然担心加电序列不匹配、他们需要 TI 的帮助来确认其测量的电源序列、对于 TI 设计而言、哪一项符合 Intel 规范。 因此,请帮助我们检查所测量的波形,并告诉我们这是否正常。

在上面,请帮助我们检查这个问题,希望很快能收到您的表格

谢谢

阿尔茨