主题中讨论的其他器件:OPA551

大家好。

我将使用应用手册

http://www.ti.com/lit/an/snoa474a/snoa474a.pdf

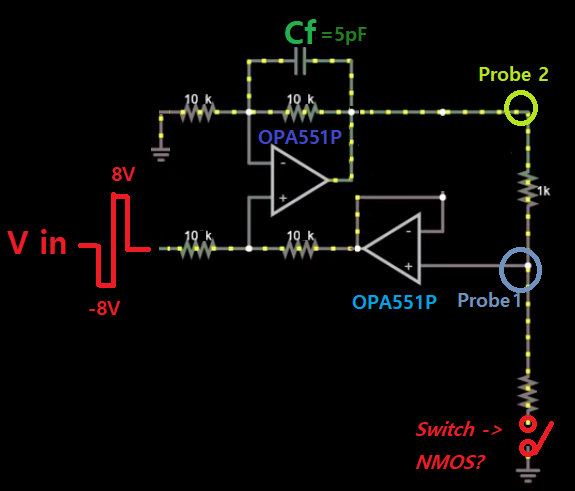

使用带有 MSP-EXP432P401R Launchpad 的 OPA551创建 Howland 电流泵。

一个周期性信号(100Hz ~ 4kHz、最大放大器= 20V)被馈入 OPA551输入。

出于个人原因、我希望断开连接到负载的 GND。

与大多数 NMOS/PMOS 应用一样、我可以使用3.3V GPIO 来打开或关闭电路。

但是、由于 OPA551提供高电压输出和电流(也是正+和负-)、我不确定是否可以为我的情况应用 NMOS/PMOS。

我可以在需要时使用 NMOS 或 PMOS 断开 GND 吗? 如果是、您可以推荐 TI 的哪一部分?

功耗、封装尺寸或价格都无关紧要。 我希望产品能够处理这种高电压和电流。

此外、我更喜欢可以立即组装到试验电路板上的封装。

或者、如果有更好的解决方案、而不是使用 NMOS/PMOS、考虑到我正在使用 MSP-EXP432P401R Launchpad、我也希望听到其他方法