您好 TI

图8-1所示。 5V 输出 TPS54561 TPS54561数据表的设计示例修订版 G、

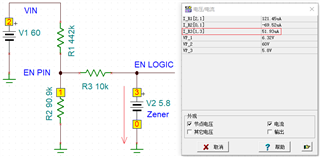

启动输入电压(VIN 上升)= 6.5V

停止输入电压(VIN 下降)= 5V

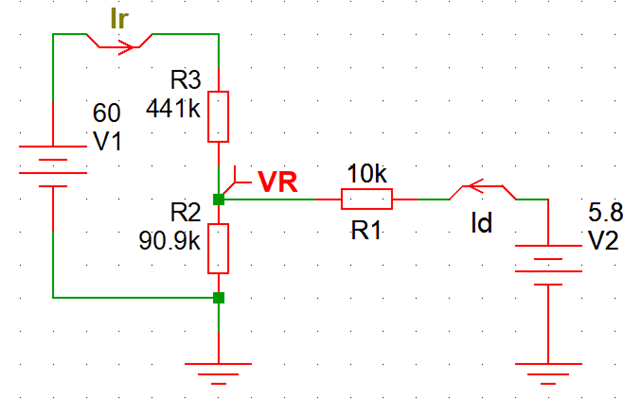

然后、通过等式45和46、我们得到 Ruvlo1=441k 和 Ruvlo2=90.9k。 因此 r1=442k 和 r2=90.9k。

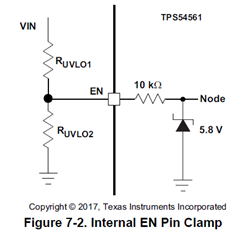

但是、我们还将得到 EN/UVLO 引脚电压为60*90.9/(442+90.9)=10.23V、此10.23V 高于 EN/UVLO 引脚内部5.8V 齐纳二极管电压。 我认为这不是良好的工作条件。

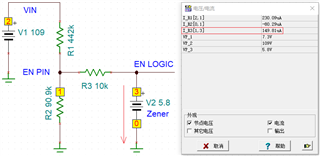

如果输入电压为34V,我们将得到 EN/UVLO 引脚电压为34*90.9/(442+90.9)=5.799,低于5.8V 齐纳二极管电压。

图8-1. 5V 输出 TPS54561设计示例旨在 支持7.0V 至60V 的输入电压、但35V 至60V 不是良好 的工作条件。

我们如何解决这一矛盾?

谢谢、

金森