主题中讨论的其他器件:TPS51120、

大家好、

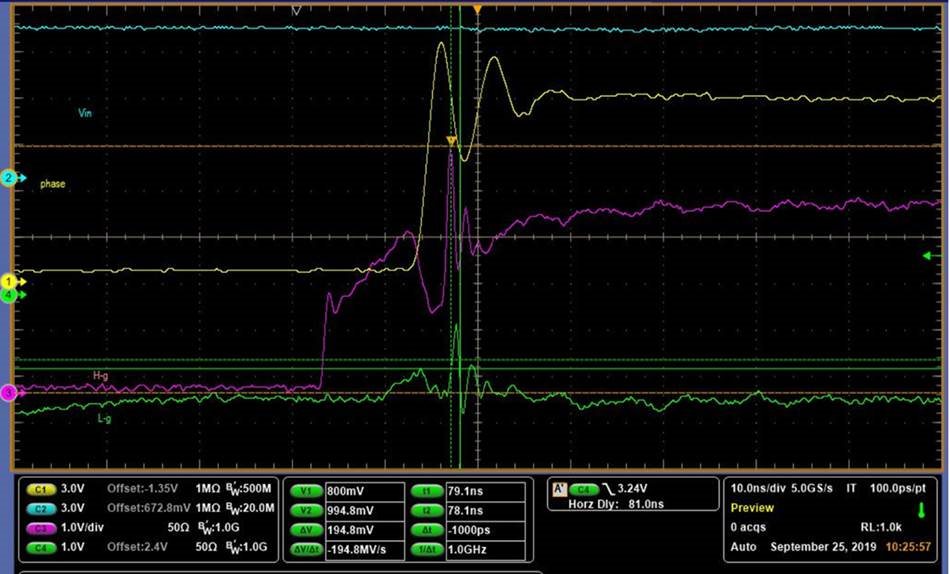

我们的客户将 CSD87350Q5D 与 TPS51120搭配使用、当他们向输出端添加11A 负载时、两个 H/L Vgs 上都会出现浪涌、这可能会导致 H/L FET 同时导通、浪涌持续时间大约为1ns、请参阅下面的波形。

根据数据表、 CSD87350Q5D 的导通延迟时间为7ns (Q1)和8ns (Q2)、但两者都是类型值、我们是否具有最小值? 1ns 浪涌是否会导致 H/L FET 导通并对电路造成损坏? 请就此发表一些评论吗?

谢谢。

此致、

刘利维亚