主题中讨论的其他器件:TPS62133、

您好!

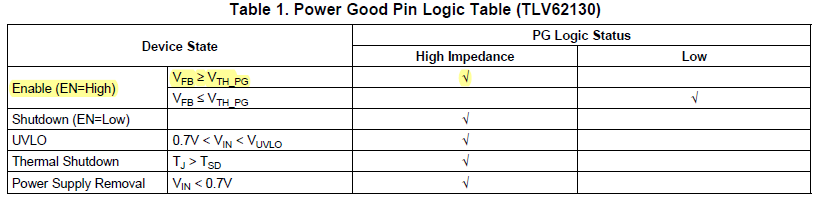

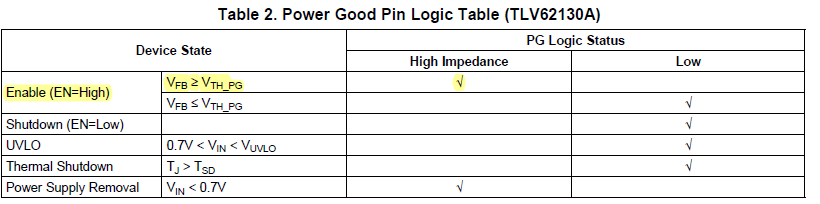

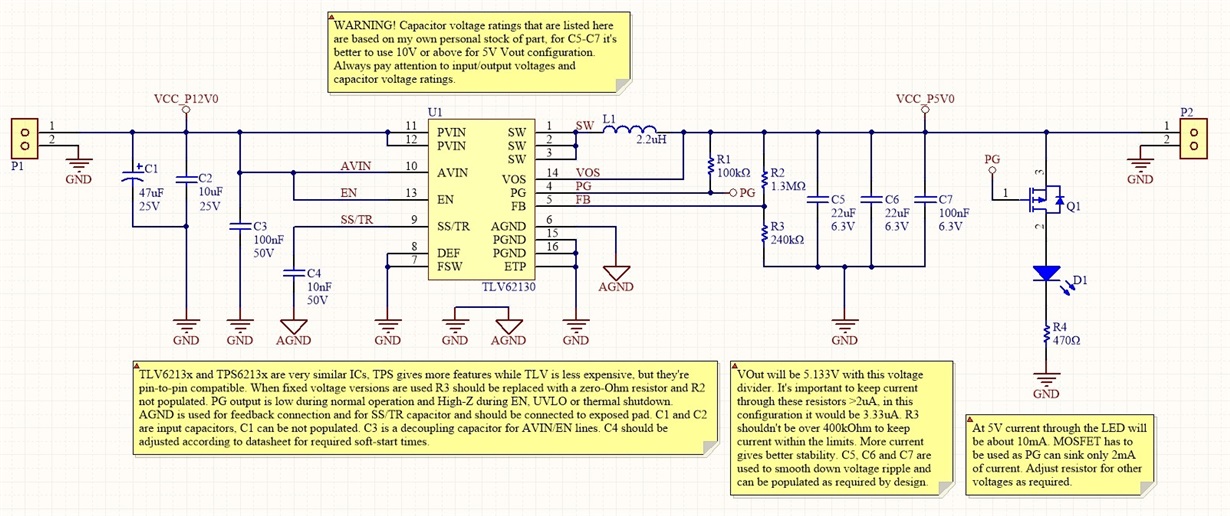

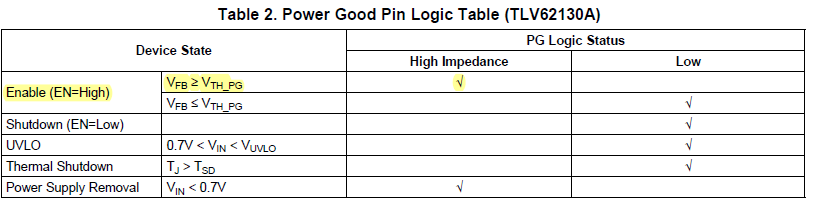

我遇到了 TLV62130的 PG 引脚问题。 根据手册:'对于 TLV62130、当器件由于 EN、UVLO 或热关断而关断时、它是高阻抗。' 在我的设计中、它通过100kOhm 电阻器上拉至 TLV62130的输出、但在我的设计中、PG 始终保持高电平、即使 IC 正常工作、也不会通过 EN 引脚或 UVLO/热关断状态下关断。 TPS62133连接到同一电路板时、可以毫无问题地控制 PG 引脚、它会在正常工作期间将其拉低。 我的设计只是基于 TLV6213x EVM 模块和器件数据表的通用设计。 谢谢!