一位客户正在设计基于2.3kW (390V/5.9A)功能的 UCC28070。

※Ω 输入为200V 交流

但问题正在发生、VDS 振铃很大。

我的问题是以下两点、请告诉我任何建议;

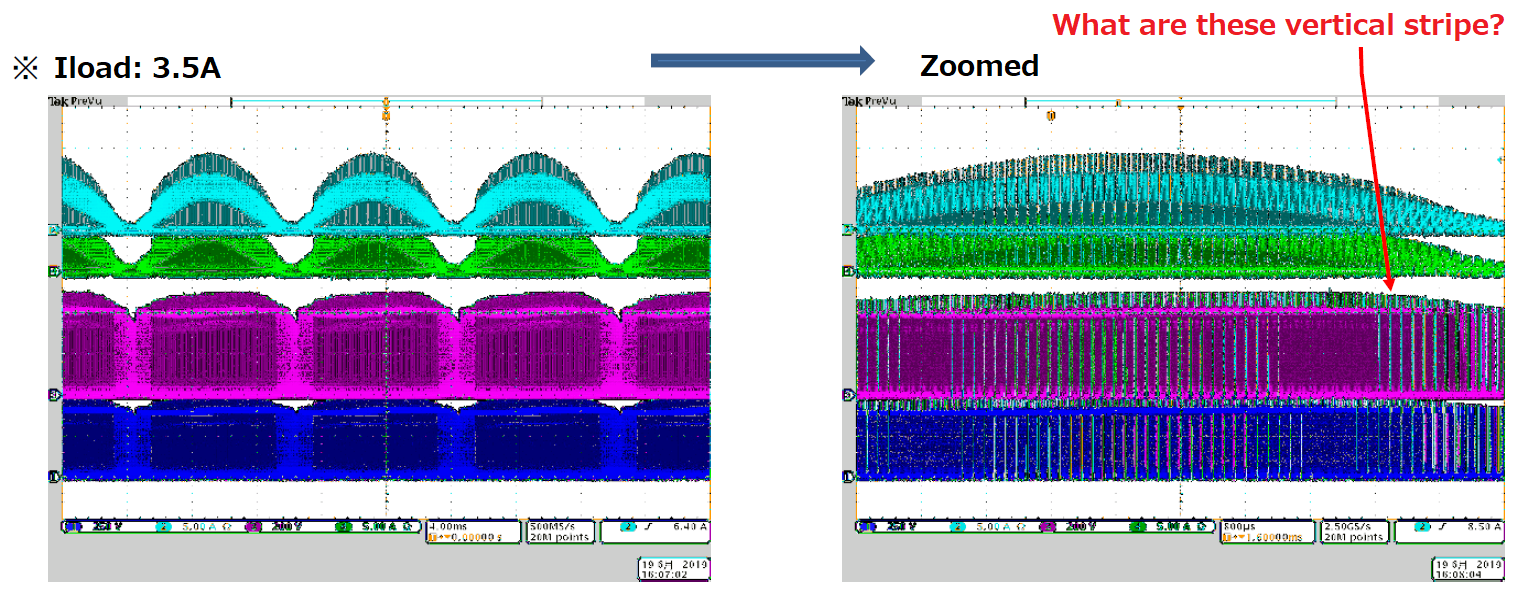

①When μ A 负载电流增加至"0A→0.5A→1A→--→5.9A"并且通过示波器进行测量、波形为明显的垂直条带。

低于垂直条带的原因是什么?

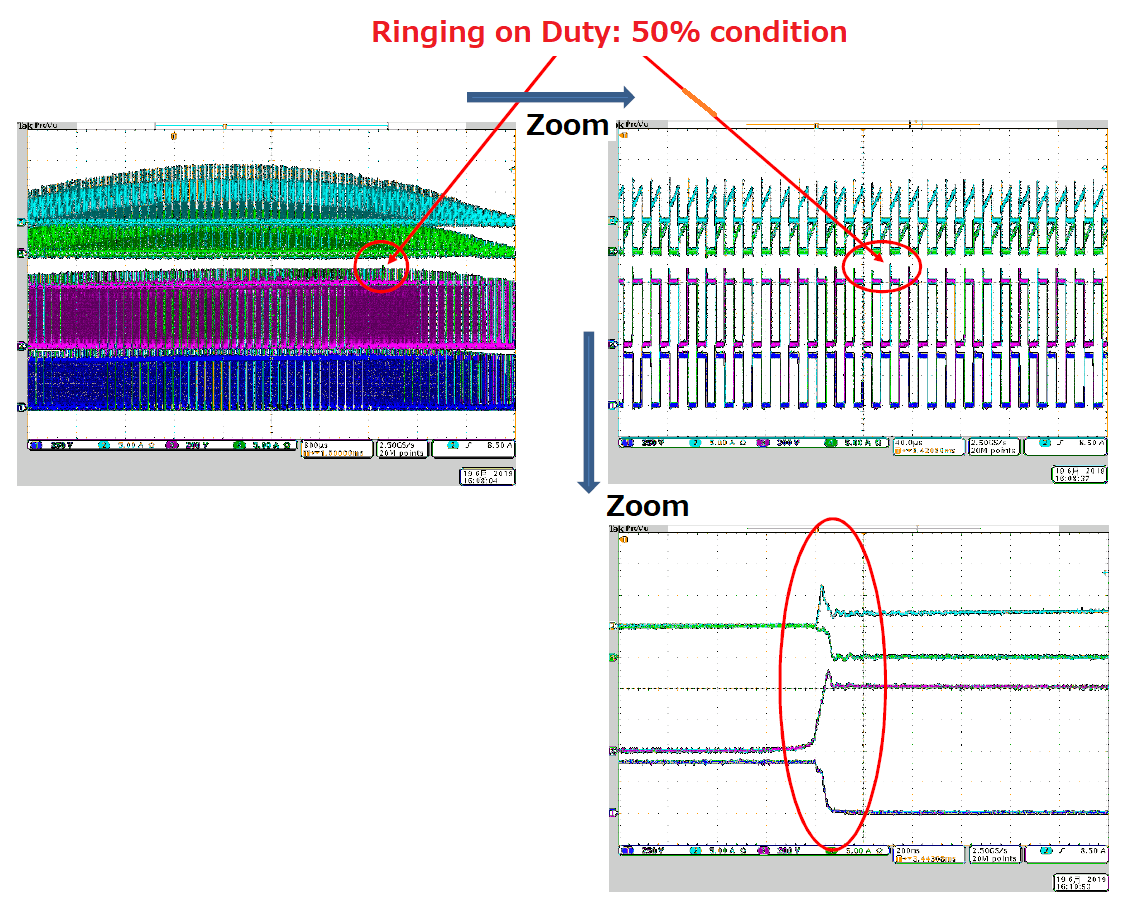

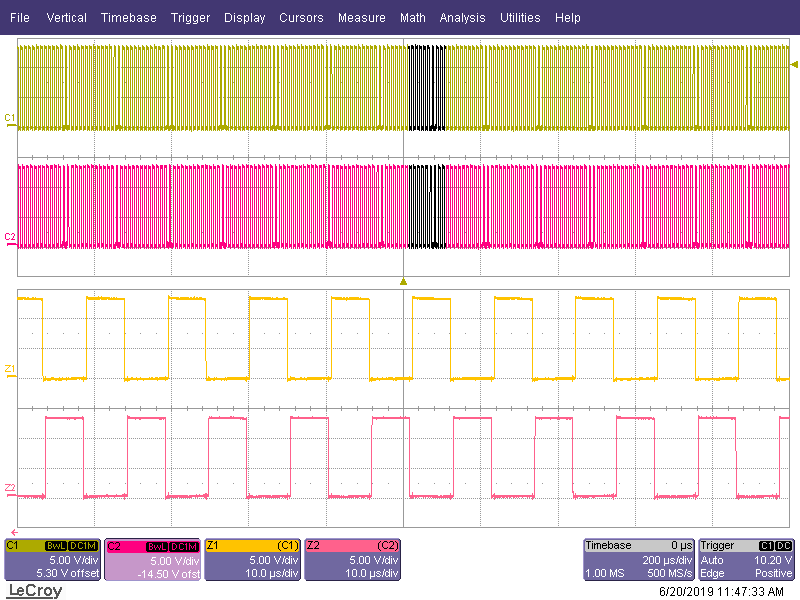

占空比的②When μ s 时序超过50%(小于50%→50%)、会发生较大的 VDS 振铃、而较大的电流会产生较大的 VDS 振铃。

※如果是"超过50%→低于50%"则没有问题。

请告诉我将 VDS 振铃增加50%以上的原因。

此外、是否有任何减少振铃的想法?

此致、

Satoshi