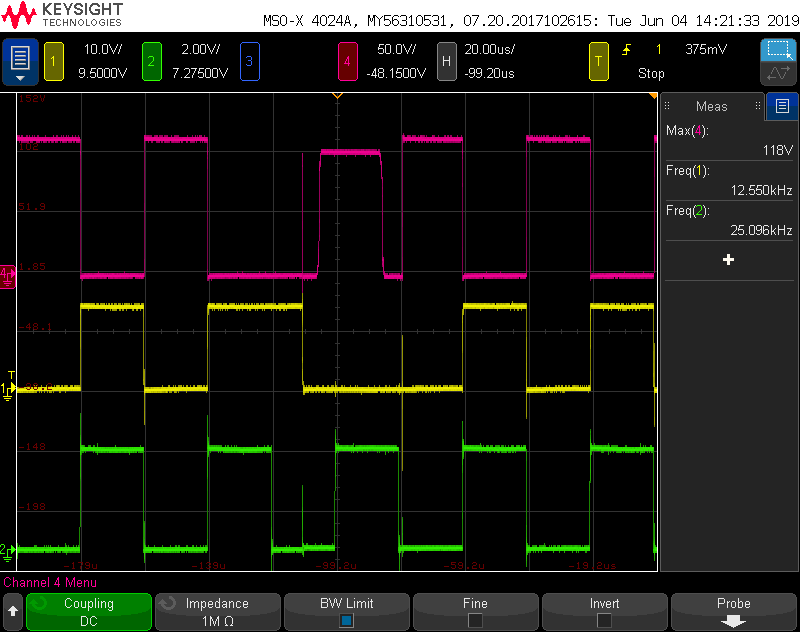

我使用两个驱动器来控制 H 桥的两侧。 如果这些驱动器存在输出偶尔锁存并保持其状态、从而使其与相应的 HI/LI 输入不匹配的问题、则会出现这种情况。 [请参阅随附的图片:绿色- LI、黄色- LO、粉色- HO。]

当 LI 输入转换为低电平但 LO 输出保持高电平时、会出现主要的重复性问题。 HI 输入是 LI 的反向输入、此时也不会改变。 在输入变化(>1us)后的一段时间内,输出会发生变化,但会错过下一个边沿,依此类推。 这会持续几个周期、然后驱动器再次赶上。

PWM 驱动信号以25-26KHz 的频率运行、LI 和 HI 输入之间的死区时间为50ns。 我已经尝试过:更换所有硬件、向 LI/HI 输入添加电容器、增加电源电容器的电容。

从数据表中、我看不到 LO 输出在 LI 输入为低电平时变为高电平的任何情况。 有人能解释为什么会发生这种情况吗?

电源轨不会下降、驱动器的输入也不会出现任何问题。

请参阅下面的原理图: