主题中讨论的其他器件:TPSM846C24、 SN74LVC2G07

大家好、

我只想快速仔细检查 EN 引脚的输入接口。

EN 引脚是否接受3.3V CMOS 输入?

此致、

Itoh

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我只想快速仔细检查 EN 引脚的输入接口。

EN 引脚是否接受3.3V CMOS 输入?

此致、

Itoh

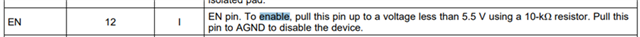

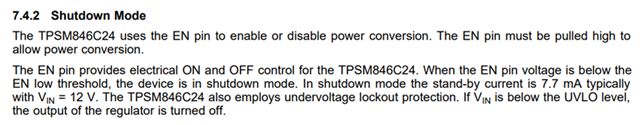

TPSM846C24的 EN 引脚具有 大于0.8V 的高到低阈值、以及小于1.3V 的低到高阈值、典型迟滞为170mV、最大额定电压为7V。 它与1.8V、2.5V、3.3V 和5V CMOS 推挽逻辑电平兼容

您好、Peter-San、

我认为 TPSM846C24不兼容 CMOS 推挽逻辑。

在 下面的线程中、您提到 EN 引脚具有到 BP6的弱上拉电阻。

我的客户尝试使用1.8V LDO 输出启用 TPSM846C24、然后 LDO 输出电压稳定至~3.5V。

我认为集电极开路/漏极输入是强制性的、CMOS 逻辑不可用于控制此器件。

我的客户 在 LDO 输出端添加了一个晶体管以解决该问题。 晶体管上拉至 BP3。

此权变措施是否正常?

(客户还尝试添加集电极开路缓冲器 SN74LVC2G07、但它不符合序列要求。)

此致、

Itoh

我相信我不会在这里遵循您的方法。

您描述了如何使用1.8V LDO 输出驱动 EN 引脚。 它们是否直接将1.8V LDO 连接到使能引脚、而在1.8V LDO 上除了使能引脚上没有其他负载、从而使 EN 上的10μA Ω 上拉电阻器将 LDO 驱动到负负载条件?

如果驱动逻辑存在内部10μA μ A (最大值)使能上拉电阻问题、则在使能引脚上添加50 100kΩ EN 至 AGND 负载电阻器将防止使能引脚上的上拉电流对1.8V 电源进行反馈。 这通常不是问题、因为为推挽驱动器供电的1.8V 电压轨在没有添加 EN 至 AGND 电阻器的情况下通常具有超过10μA Ω 的负载。