主题中讨论的其他器件:TPS63710、 LP5907、 LP5912

大家好、

不幸的是,问题仍然存在。

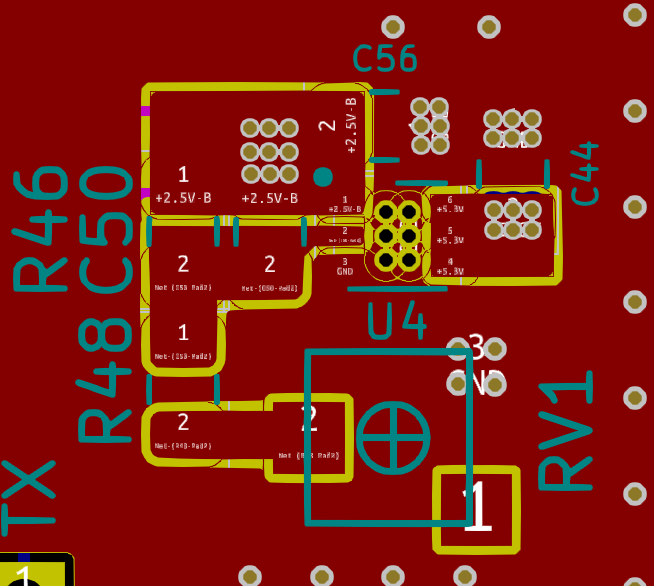

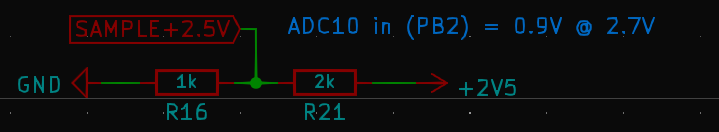

这种混乱的第一部分 就在这里

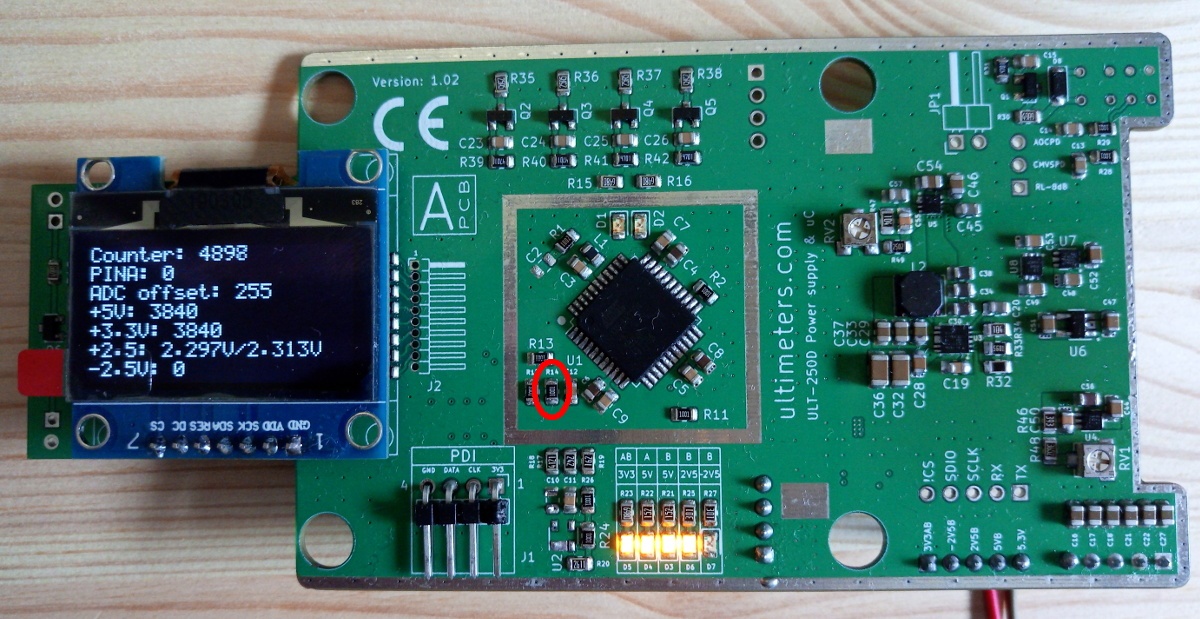

更糟糕的是、我已经对 PCB 进行了一些改进(至少我认为我已经改进过)、并尝试了 LDO TPS7A3725的固定版本(2.5V)、但我运气不好。

起初、一切都运行了几分钟、然后开始了颤抖和随机行为。

我处于死区状态 几个月的时间、我遇到了 LDO 不稳定问题。 我想的最后一件事...

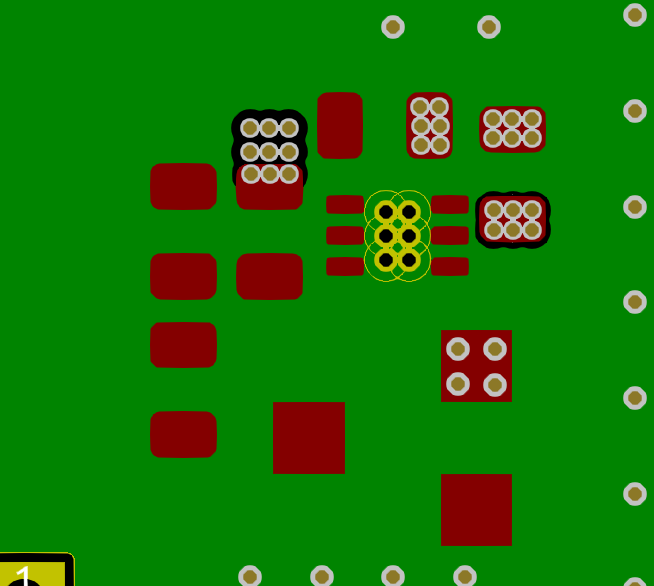

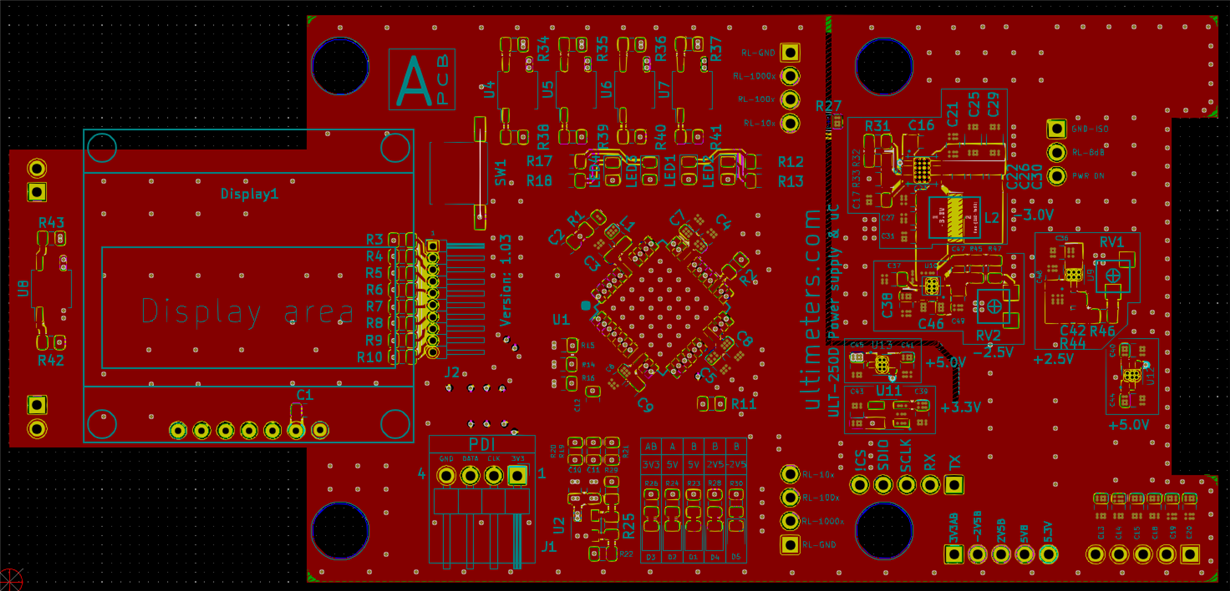

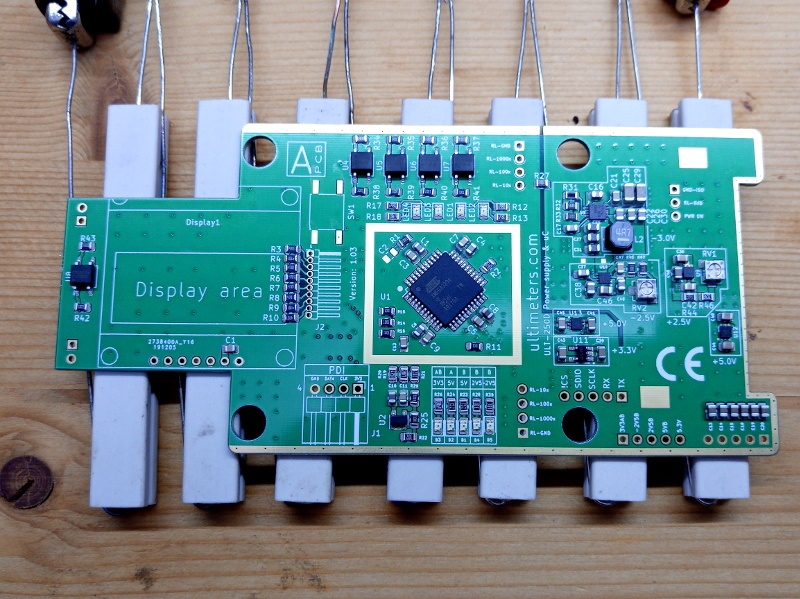

这是 TPS7A37XX 周围的6层 PCB、可看到顶层焊锡膏区域

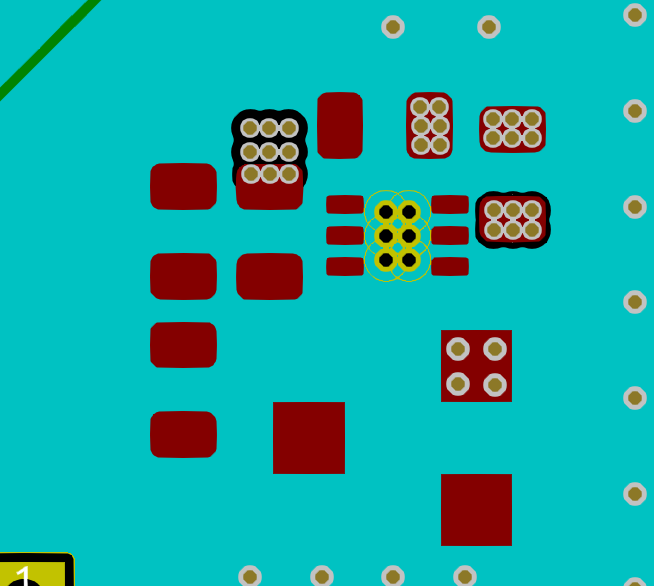

该^是底层。 接地平面清晰可见。

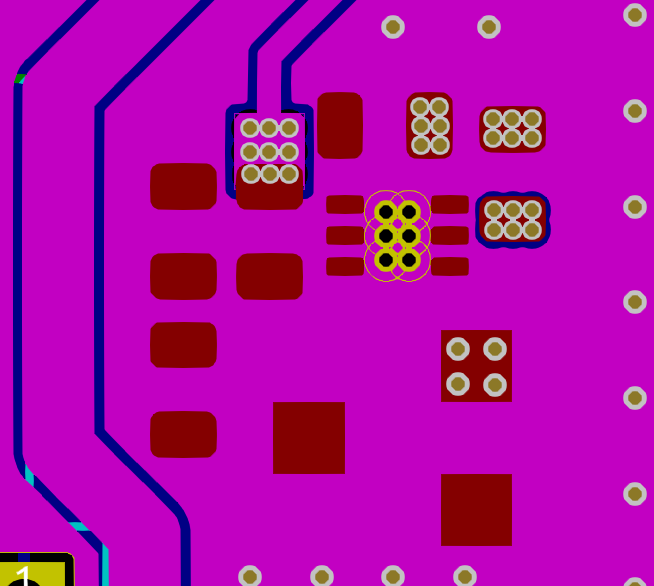

该^是内层4。 就像底层一样、接地层是青色区域。

该^是内层3。 这里没有接地平面。 您看到的蓝色区域(不靠近边缘)是为 TPS7A37XX 供电的+5.3V 电源轨。

该^是内层2。 同样、接地平面是主要的。

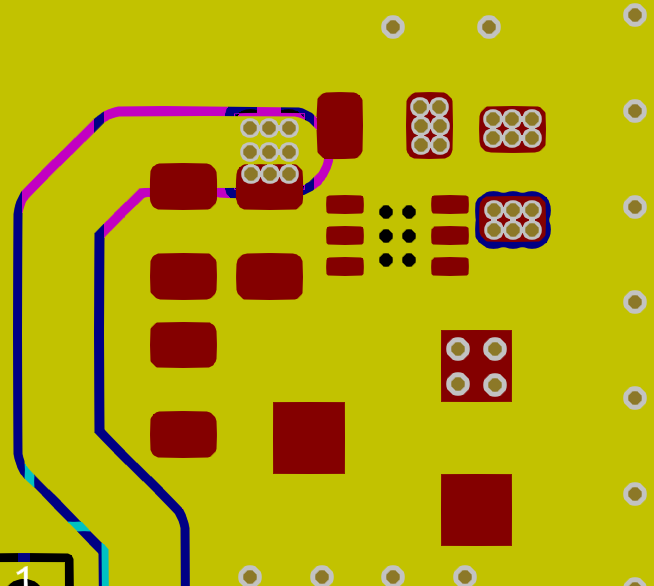

该^是内层1。 接地层位于反馈环路布线下方。 黄色迹线向下将 TPS 的输出端连接到引脚接头。

该^是顶层。

该^是 TPS 的固定版本、根据 DS 的要求、FB 引脚通过 MLCC 10nF 去耦以进一步降低输出噪声。

我发现很奇怪的是、2x LP5912、1x LP5907和 TPS63710逆变器 SMPS 没有遇到任何问题。

这是否可能是固有的不稳定问题? 我已经为第一个原型 PCB 花费了200美元、为最后一组 PCB 又花费了200美元。

MLCC 电容器的关键选择如何?

DS 在 p 8.1.1中指出:"在多个低 ESR 电容器并联的应用中、COUT×ESR<50 nΩ F 时可能会发生振铃。" 您可以解释一下吗?

我已为输入和输出选择此电容器: 单击此处。

你有什么建议吗? 我是否应该寻找替代产品?

此致

Manos Tsachalidis