主题中讨论的其他器件: TPS62866

大家好、

这是客户提出的一个问题。

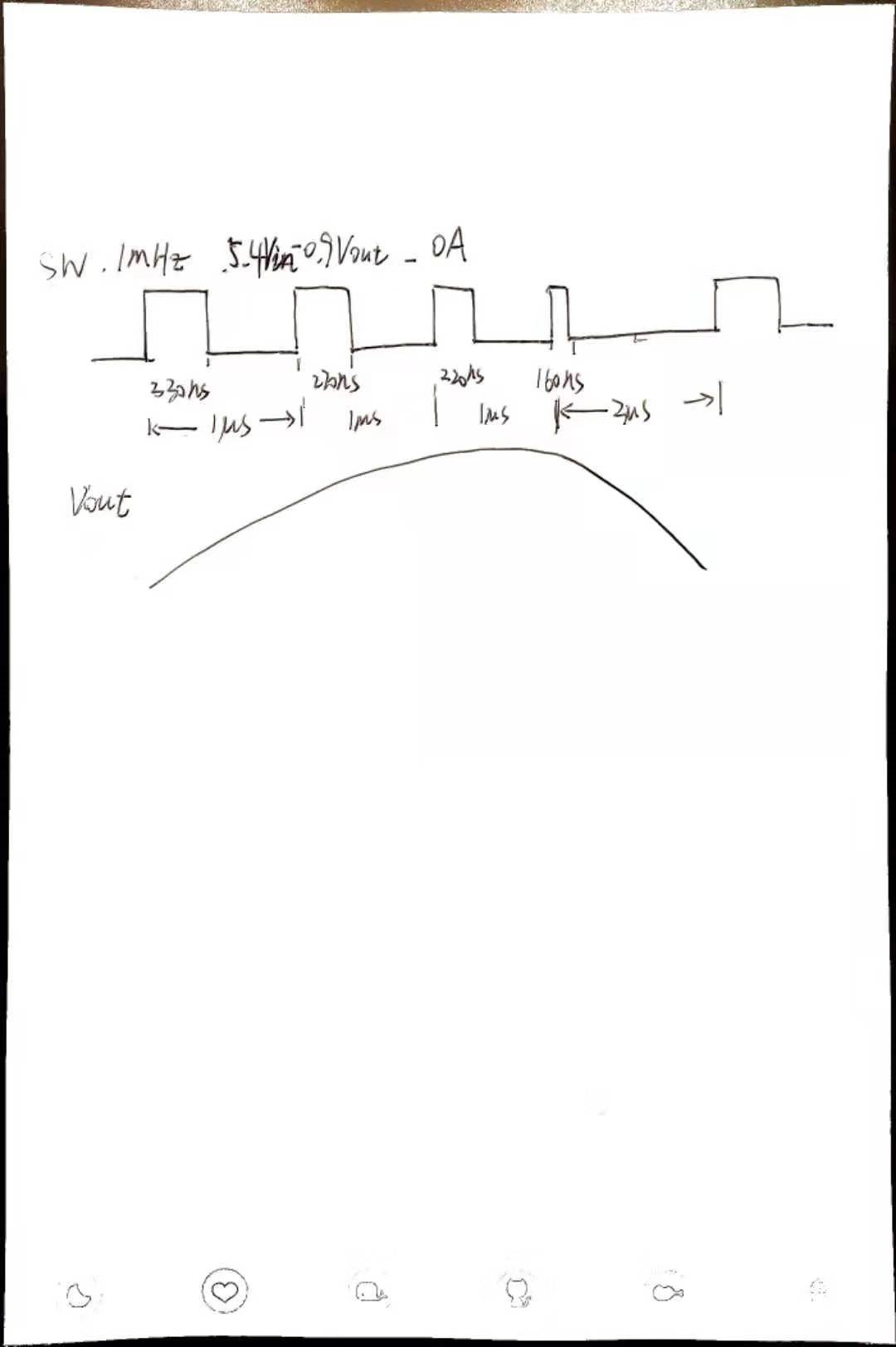

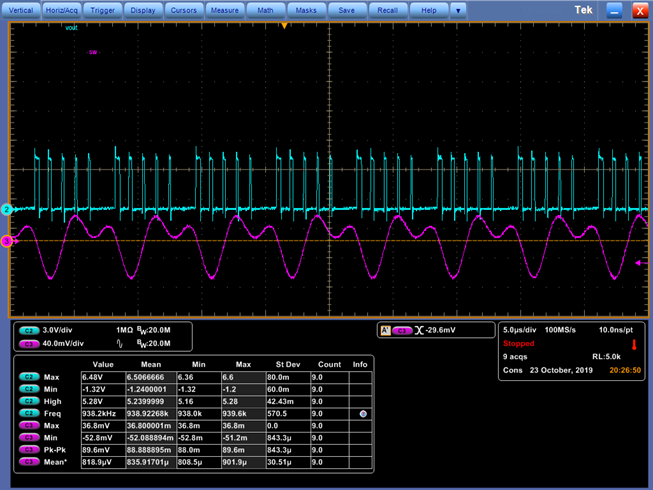

5.4V 输入至0.9V 输出、Iout=0A、Fsw=1MHz、 您可以在 SW 波形下方看到 占空比变化。

a:将负载增加到1A、占空比变得稳定。

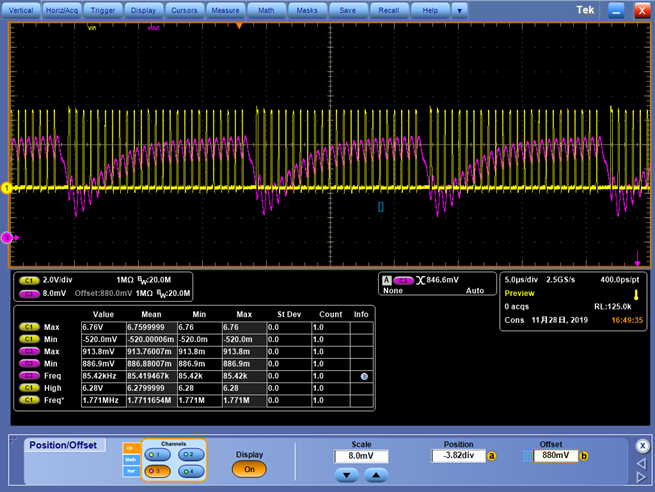

b.将 Vout 更改为低于0.9V、问题始终 存在。 将 Vout 更改为高电平值、例如1.2V、无问题。

c.在 COMP 引脚与 GND 之间添加15pF 电容、负载变得稳定。

D.将 Vin 降至5.4V 以下、占空比稳定。

所以这个问题似乎与职责有关。 我怀疑它最初与 COMP 上的噪声相关、但它无法解释为什么会出现更高的输出电压和更低的输入电压问题。 从波形来看、它似乎与 Ton-min 有关、但不确定如何解释波形。

请添加您的意见。 谢谢。

BRS

假设