尊敬的团队:

我们的客户在以下系统用例中使用 UCC28631:

- 输入电压:350至450V

- 输出功率:100W

- 标称输出电压:24V

我可以通过电子邮件共享客户的原理图和设计文件(Excel) 还有一些有关变压器的更多详细信息。

在较小的负载(5kOhm 的虚拟负载)下、它们会看到以下问题:

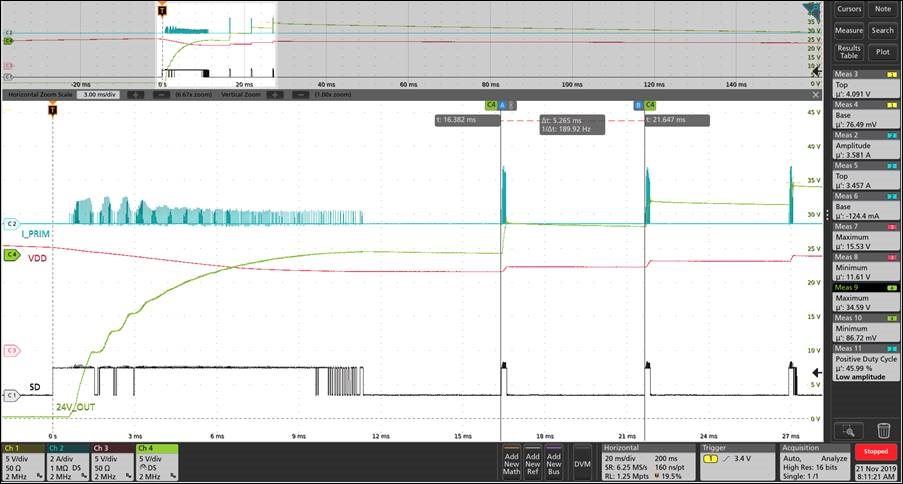

"开关频率和占空比突然变得太大、就好像它们停止被调节一样、没有明显的原因发生这种情况。 下面显示的示波器图(CH1:SD、CH2:I_Prim、CH3:VDD、CH4:VOUT)描述了我尝试描述的行为。

电源启动和输出调节至24V。 突然开关停止、电压开始下降、当稳压回升时、开关频率已经为120kHz、占空比为~60%。

这种脉冲的“突发”持续,间隔为5ms,增加输出电压,直到 OVP 开始生效。 放大后的示波器图显示误差代码为20、还显示了占空比和开关频率的变化情况。"

不同的测试点:

- 向输出端添加680uF 电容也有助于降低发生“杂散行为”的频率,但仍然会发生

- 50ohm @ 200V 在大部分时间都能工作。 增大输入电压将使问题再次出现。

请帮助我们了解什么问题可能会导致问题?

谢谢、致以诚挚的问候

Martin

CH1:SD、CH2:I_Prim、CH3:VDD、CH4:VOUT

条件:

- Rload = 5kOhm (外部施加)

- VIN ~= 120V (输入电压实际上已上升至350V、但电源已在120V 时启动)