主题中讨论的其他器件: LM5116

您好!

我们在48V 至28V (最大2A) SMPS 设计中使用 LM5116。 在特定负载条件下(~150-300mA)、电路似乎变得不稳定、并且通常会导致低侧 FET 发生故障。 我们怀疑我们的布局可能是问题的根源、但我们能够使用 LM5116EVAL 板重现此问题。 有什么想法会导致这种情况发生?

谢谢.... Alan

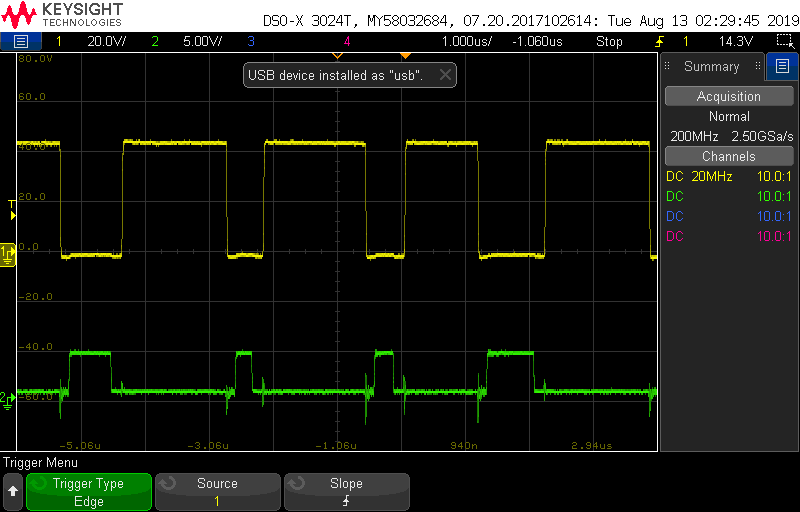

黄色: 电感器输入电压

绿色:下部 FET 栅极驱动

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

我们在48V 至28V (最大2A) SMPS 设计中使用 LM5116。 在特定负载条件下(~150-300mA)、电路似乎变得不稳定、并且通常会导致低侧 FET 发生故障。 我们怀疑我们的布局可能是问题的根源、但我们能够使用 LM5116EVAL 板重现此问题。 有什么想法会导致这种情况发生?

谢谢.... Alan

黄色: 电感器输入电压

绿色:下部 FET 栅极驱动

Tim 您好-感谢您回答我的问题!

更新了: 我能够通过将 SW 电感器降低到15uH 来解决漏极栅极脉冲问题-但不确定这为什么有用。 ckt 行为得到了很大改善、但仍然有点古怪(见下文)。

随附了 Schem、Webench 报告和 Quickstart。

谢谢 Alan

e2e.ti.com/.../LM5116_5F00_quickstart_5F00_28V_5F00_spreadsheet.xlse2e.ti.com/.../48-to-28v-Design.pdfe2e.ti.com/.../SMPS-schem_2E00_.pdf

黄色: 电感器/开关电压

绿色:下部 FET 栅极驱动

VIN=44VDC、负载:2.0A

尊敬的 Alan:

看起来像是环路 不稳定性。 我注意到原理图中的补偿值与快速启动不同。 您可能可以减小 R74并增大 C113值。

此外、检查33uF/63V 电解输出电容的 ESR、因为这会产生 ESR 零点(也可能随温度的变化而显著变化、具体取决于 ESR 的行为)。 请注意、电解电容器在500kHz 时不提供太多的滤波、因此您可以将1uF/100V 陶瓷电容器更改为10uF/50V 电容器。

此致、

Tim

尊敬的 Alan:

输出电容器的 ESR 是多少(因为这会设置 ESR 零点)?

根据 ESR 零点、原始原理图中 COMP 和 FB 之间300pF 的 C114似乎很高、因为它在使用 R74 (36.5k)补偿电阻器进行断开时设置了15kHz 极点。 不过、我看到上面您尝试了不同的补偿值。

另一个建议是在 IC 的 VIN 引脚处添加一个小型 RC 滤波器(例如10欧姆和47nF/100V)。

在布局图中、请确保从分流器到控制器的电流感应线路紧密布线、远离 SW 和 LO 等噪声节点(如果需要、在 CS 线路上添加50ns RC 滤波器)。 反馈和补偿元件应靠近各自的引脚。 此外、陶瓷输入电容器应尽可能靠近 MOSFET。 有关更多详细信息、请参阅 LM5116数据表的布局部分。

此致、

Tim

尊敬的 Alan:

您还可以检查输入滤波器是否稳定。 要求是输入滤波器的峰值输出阻抗低于转换器的闭环输入阻抗。 因此、最坏的情况是低输入电压和满负载。

输入电解电容器需要阻尼并提供阻尼-只需检查它们是否具有足够的 ESR (您可能必须添加串联电阻)。 有关更多详细信息、请参阅此处: 直流/直流转换器中输入滤波器稳定性问题的简单解决方案

此致、

Tim

您好、Tim、

啊! 在尝试解决这个问题的同时、我们一直在烧毁大量的 LM5116s 和更低的 FET!

坏消息:已尝试过您的大多数建议、但似乎没有任何改进(尚未尝试更改输入滤波器)。 我觉得改变输出电感器已经解决了这个问题、但这一判断似乎还为时过早。

好消息(有点):我认为问题与 SMPS 何时从不连续模式转换为连续模式有关。 轻负载时、乳汁似乎稳定/正常。 随着负载增加、下 FET 上的栅极脉冲变得不稳定(某些脉冲将丢失)。 如果允许在这种情况下运行、5116和/或更低的 FET 最终将失败。 在较重的负载下、评估板上的操作变得正常、但在我们的公司设计上仍然有些不稳定(请参阅下文)。 这是 一个展示这种情况的视频(在此拍摄后不久必须更换下部 FET)。

接下来、我想我将尝试在下部 FET 上添加一个缓冲器。 希望上述行为能让您了解如何解决此问题。

谢谢 Alan

更新: 在尝试许多方法来纠正缺少的较低栅极驱动脉冲后,我尝试将 IC 从二极管仿真模式切换到完全同步模式。 这似乎解决了从 DCM 模式切换到 CM 模式时出现的栅极驱动缺失问题。 我不确定 DEMB 引脚的预期用途是什么。 您能解释一下吗?

对于 DEMB 引脚、数据表规定: 对于启动至预偏置负载、请在 CSG 连接处将该引脚接地。 什么是"预偏置负载"?

新问题: 现在电源似乎基本上正常工作(仍有一些 PWM 异常、请参阅上图)。 但是、当施加1.5至2A 的负载时、较低的 FET 和/或5116将发生故障。 我尝试在其 D-S 和 G-S 引脚上添加 TVS 二极管。 它是一个80V FET。 源电压为48V -可能需要更高的额定值? 仅供参考、我们在 48V 至12V 的设计中使用相同的设计、IC 和 FET、没有任何问题。 这个方面让我非常怀疑这些问题与布局有关-但我尝试了很多修改、但没有做任何改进。

上一个问题的迟来答案: 输出电容为:Panasonic 63SXV33、33uF、63V、ESR=25mohms。

感谢您的帮助.... Alan

尊敬的 Alan:

DEMB 引脚的功能可实现低侧 FET 的二极管仿真、从而实现 DCM 运行以提高轻负载下的效率。 如果在启动前输出端存在电压、则会发生预偏置负载。 更多详细信息、请参阅数据表的第7.4.1节。

在您的情况下、连接到控制器的 SW 和 DEMB 线路上可能会产生噪声、从而影响二极管仿真模式下的电流感应。

通常、没有理由将栅极驱动器钳制到 FET。 控制器的正常栅极驱动振幅实际上是 VCC 电平(如果使用外部偏置轨、则为外部 VCC)、这远低于 FET 的20V 最大栅极驱动。 就 VDS 电压而言、高侧 MOSFET 导通时与开关环路的寄生电感相关的前沿尖峰。 如果尖峰低于 FET 和控制器的额定值、这是可管理的。 通过将一个陶瓷电容器(例如10-100nF)放置在非常靠近 FET 的位置、可最大限度地减小该值、从而减小开关电源环路面积。

此致、

Tim

您好、Tim、

已将开关 FET 替换为250V (Vs 80V)器件。 现在 FET 故障要少得多。

电路仍然非常不稳定。 似乎可以正常工作、但想弄清楚是什么导致了这种古怪的行为。 它可能与布局有关,但是

已尝试不同的同步信号测试-没有任何改进。 已尝试板载内部5116时钟(无 SYNC)、PCB 生成的 SYNC、通过实验室发生器实现的 SYNC、各种频率、占空比、幅度。

学习了几个小问题: 1)如果同步占空比小于49%、电路停止调节(但看起来稳定)。 2) 2)某些同步频率似乎会使电路稳定、但与负载相关。

尝试的东西太多了、现在就解决这个问题了。 如果出现新问题、将重新打开。

谢谢。。。 Alan

绿色: FET/电感器波形、蓝色:低 FET 栅极驱动、粉色:同步

以上单次触发: