Other Parts Discussed in Thread: LM5105

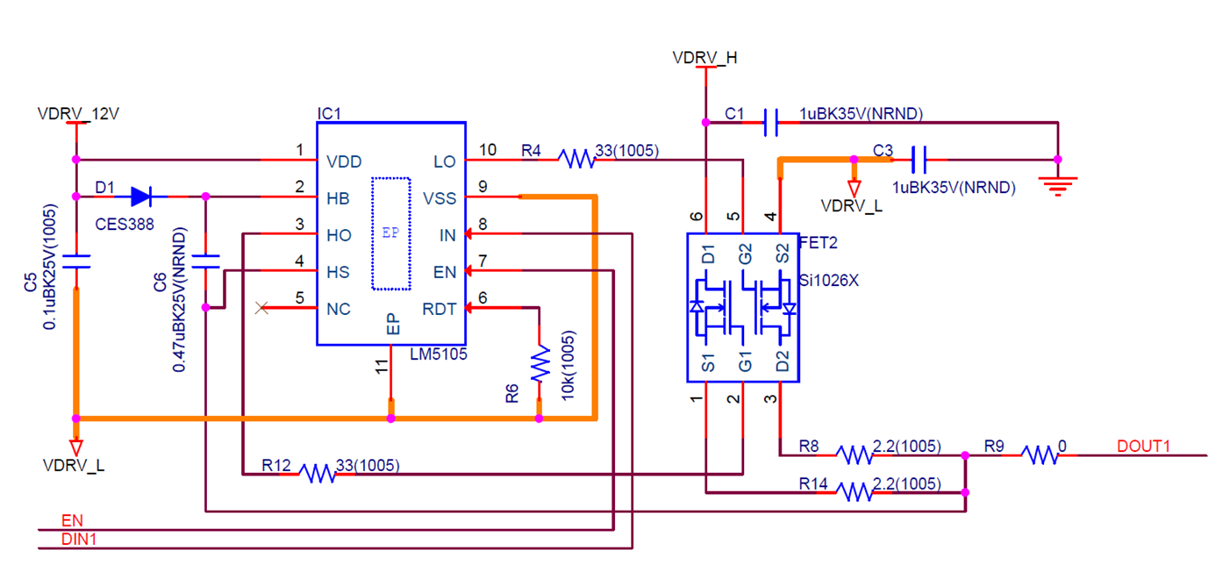

我们使用 LM5105设计了半桥 MOSFET 驱动器电路、如图1所示。

我们尝试以60Hz 的流低、高侧16.6ms 和低侧1.8μs 连续驱动。

其他信息如下所述。

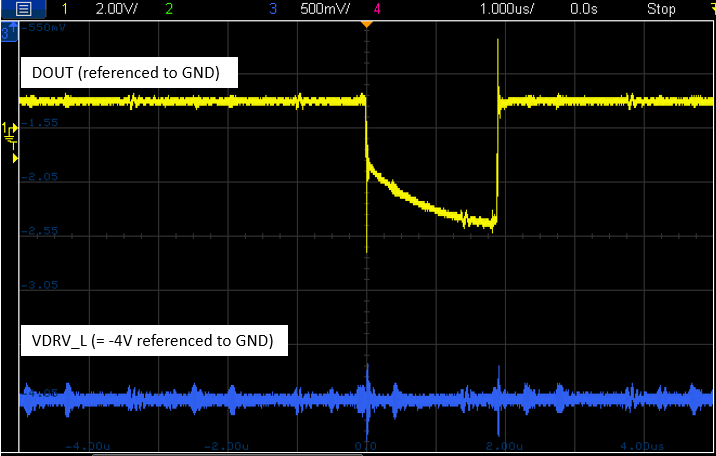

VDRV_L:该电路的参考电压(非 GND)

VDRV_H:最小5V、最大15V (由用户可变)

VDD:12V

VSS:0V (VDRV_L)

EN:3.3V

DIN:高=3.3V、低=0V

DOUT 未连接到任何负载。

我们实际上执行了这样的驾驶并发现了问题。

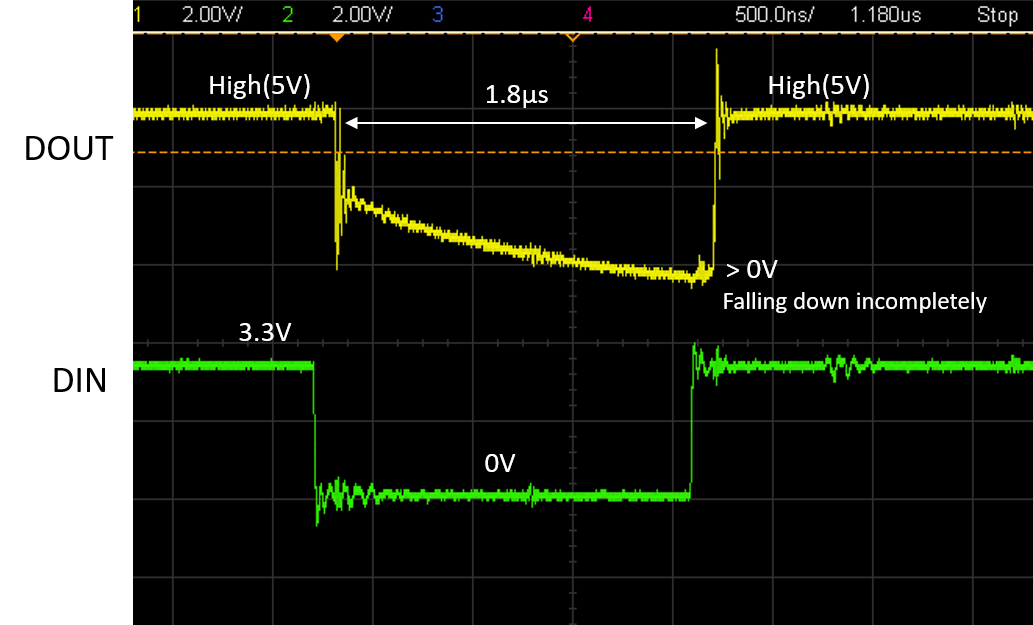

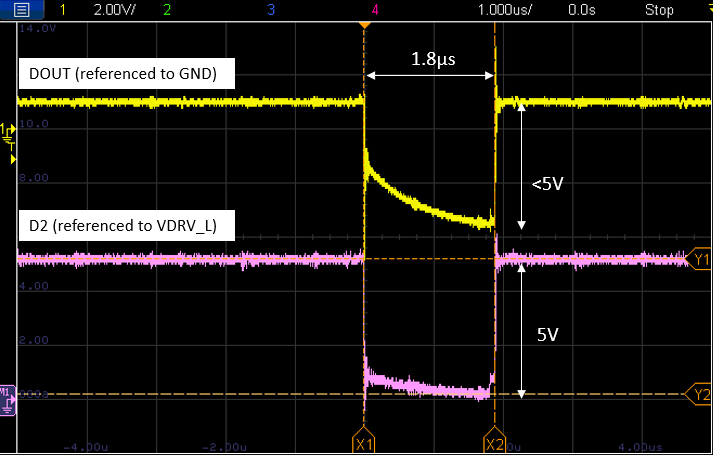

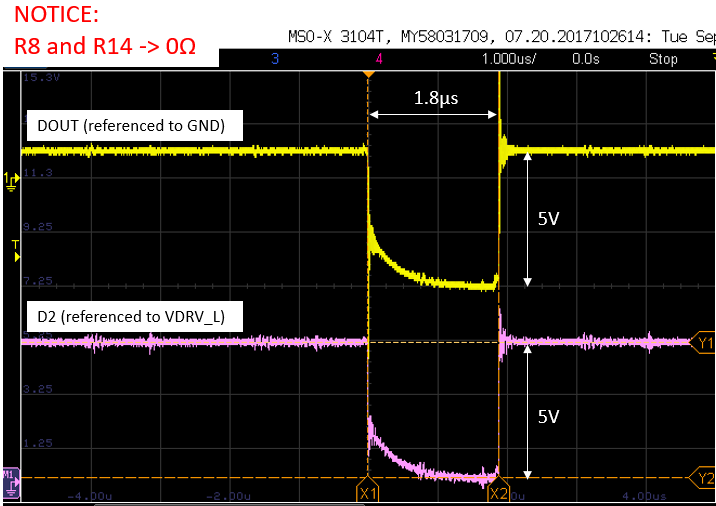

DOUT 的波形下降得非常慢。

1.8μs 图2、完全为低电平所需的时间长于1 μ s。

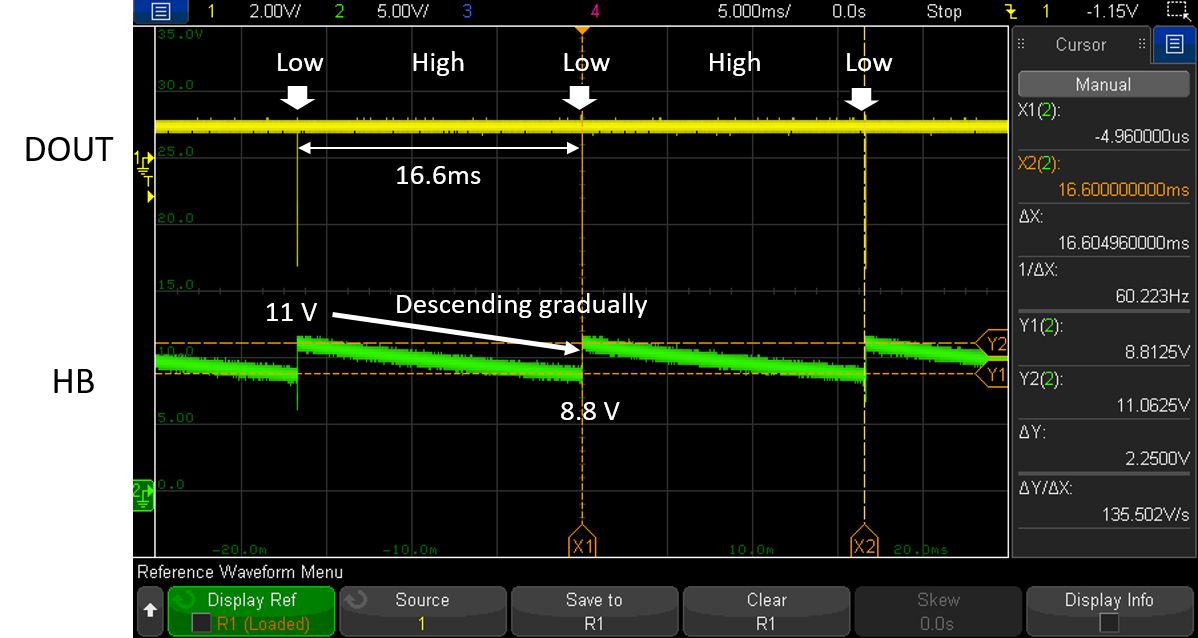

如图3所示、HB 电压在高电平期间逐渐下降。

这些问题的原因是什么?

我们希望在 DOUT 缓慢下降的情况下驱动该电路。

您对改善这种情况有什么想法吗?

谢谢你。

<<图2>>

<<图3 >>